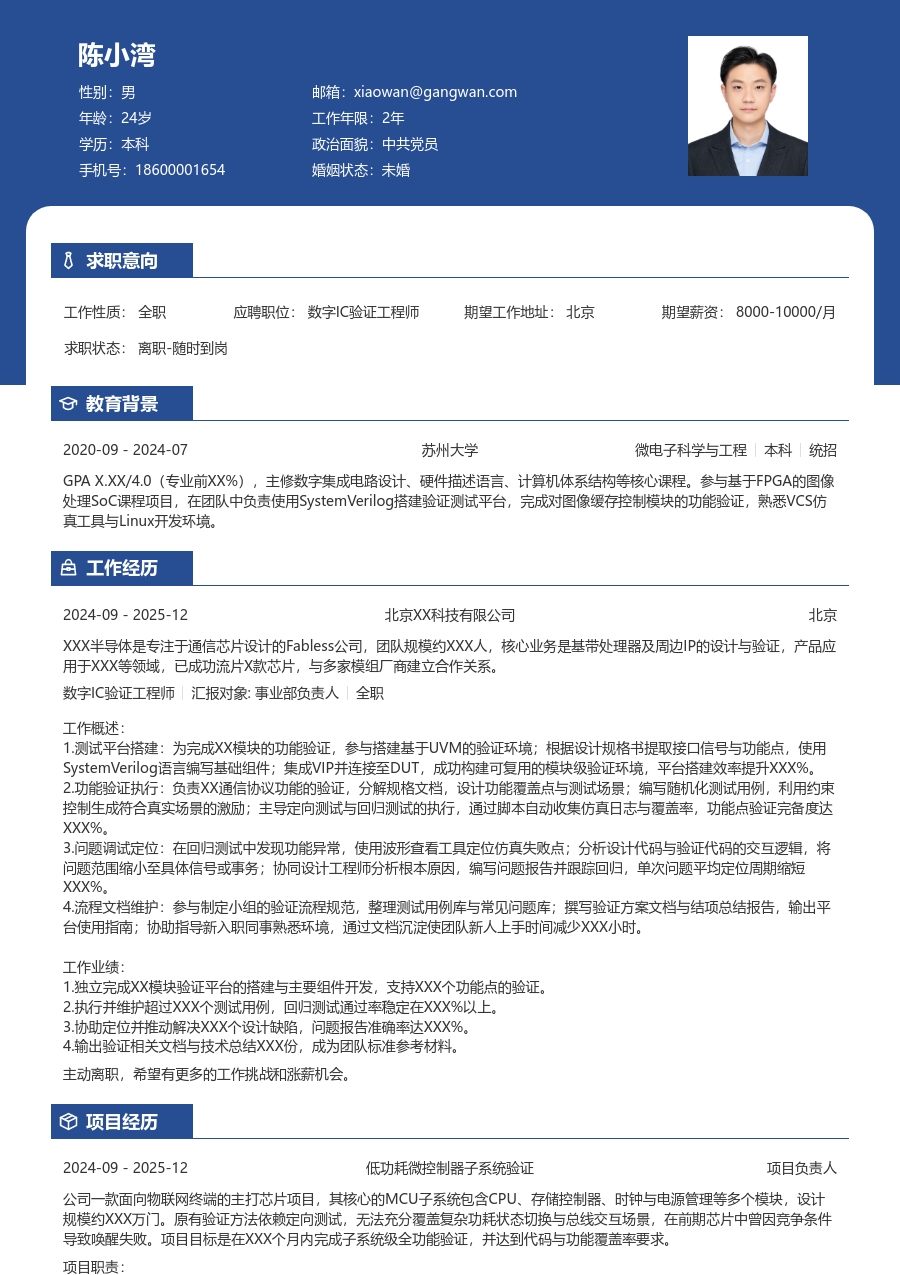

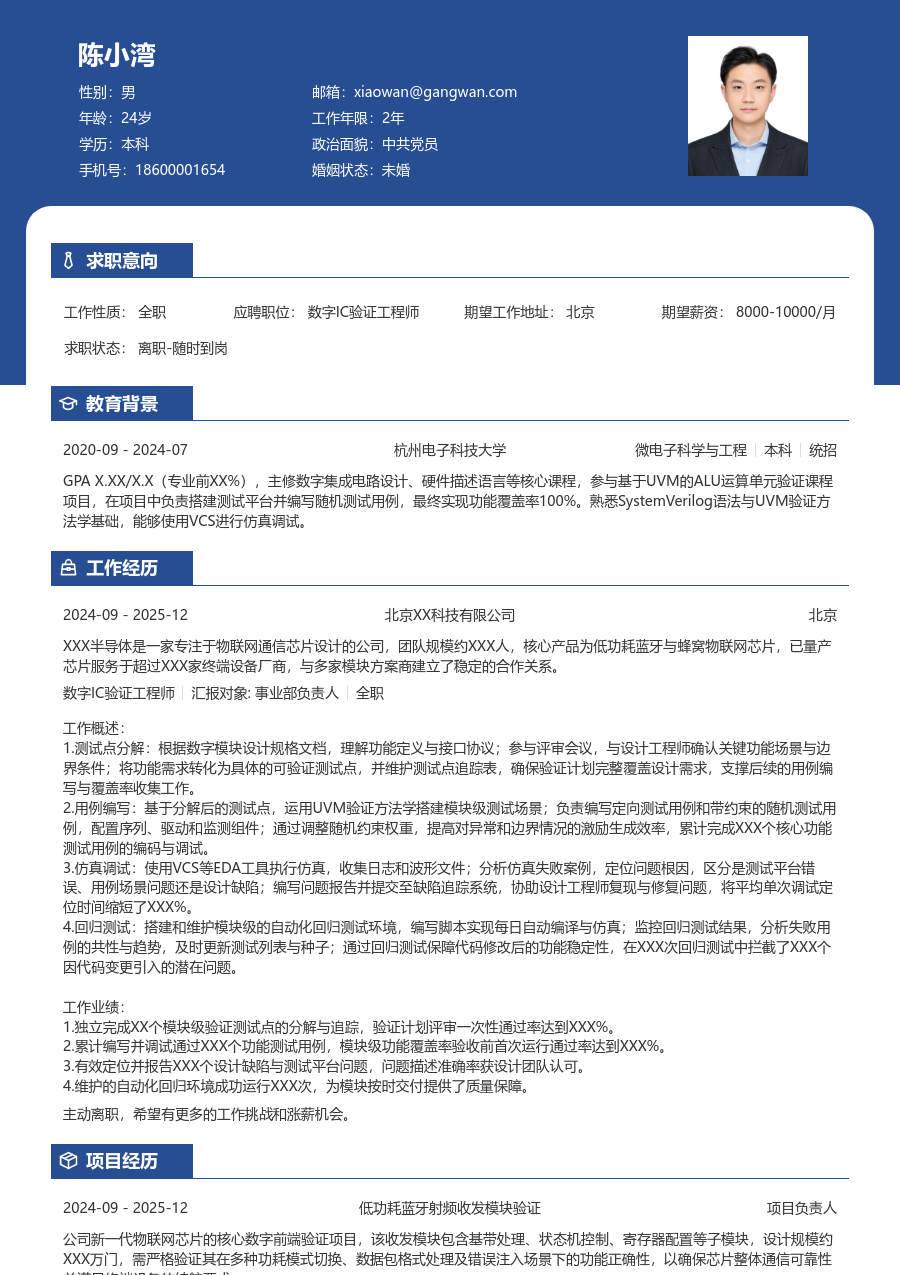

正在查看高级数字IC验证工程师轻商务简历模板文字版

陈小湾

求职意向

工作经历

XXX半导体是一家专注于高性能计算芯片设计的科技公司,团队规模约XXX人,核心业务是为数据中心和智能驾驶领域提供定制化SoC解决方案,产品已成功应用于多家主流客户,年出货芯片超XXX万颗。

工作概述:

1.验证策略制定:针对复杂IP及SoC芯片规格,制定从模块到系统的多层级验证计划;分解功能点并与设计、系统部门对齐测试目标,明确覆盖率收敛标准,通过评审与迭代将验证盲区降低XXX%。

2.验证平台搭建:主导UVM验证平台的架构设计与实现,集成第三方VIP并开发定制化组件;搭建自动化编译与仿真环境,通过脚本管理将环境复用率提升至XXX%,支持多项目并行开发。

3.测试用例开发:基于验证计划编写定向测试和随机约束测试用例,构造极端场景和错误注入案例;利用脚本自动生成并归类测试,使得验证向量对关键功能的刺激完备性达到XXX%。

4.回归测试管理:建立并维护日常回归测试集,利用服务器集群实现分布式仿真;监控回归结果,分析失败用例根因,引入自动比对与打卡机机制,将问题定位平均时间缩短XXX小时。

5.覆盖率收集与分析:使用代码覆盖率与功能覆盖率双重指标驱动验证进程;定期分析覆盖率报告,针对未覆盖点补充测试或调整约束,最终推动设计sign-off覆盖率满足XXX%的目标。

6.FPGA原型验证:负责将RTL代码移植至FPGA原型验证平台,协助软件团队进行早期驱动开发和性能评估;通过实际负载测试发现深层次时序问题,提前暴露XXX类潜在风险。

7.团队协作与培训:负责指导初级验证工程师,制定模块验证任务并review代码;编写验证方法学手册与常见问题库,组织内部技术分享,帮助团队整体问题解决效率提升XXX%。

工作业绩:

1.主导完成X颗大规模SoC芯片及XX个关键IP的验证任务,保障所有负责模块按时达成sign-off标准。

2.搭建的UVM验证平台成为部门标准模板,应用于后续X个项目,平台稳定性提升XXX%。

3.通过自动化脚本将测试用例生成效率提升XXX%,累计编写和维护超过XXX个测试用例。

4.管理的回归测试框架日均运行仿真任务超XXX个,问题发现到反馈闭环时间缩短XXX%。

5.负责模块的代码与功能覆盖率均达到并超过XXX%的门限要求。

6.在FPGA原型验证阶段提前发现并协助修复XXX个RTLbug,避免流片后重大缺陷。

7.带领X人验证小组,培养X名工程师独立承担模块验证工作,输出技术文档XX份。

主动离职,希望有更多的工作挑战和涨薪机会。

项目经历

公司首颗面向数据中心的7nm AI训练芯片,集成自研张量处理单元(TPU)及高速互联接口,芯片规模超XXX亿晶体管。项目挑战在于复杂计算单元的功能正确性验证、片上网络(NoC)的通信性能验证以及低功耗设计验证,原有验证方法无法在XXX个月内完成全芯片验证收敛。

项目职责:

1.验证规划:负责芯片中高速缓存一致性模块及DDR控制器的验证计划制定,分解出XXX个关键验证场景与断言检查点。

2.平台开发:主导上述模块的UVM验证环境搭建,集成业界标准AXI VIP,开发了总线效率监测与错误注入组件。

3.测试与调试:编写随机测试序列,覆盖各种读写交错、背压、电源状态切换场景;使用波形调试工具与日志分析脚本,快速定位并提交XXX个设计缺陷。

4.性能验证:构建系统级性能验证场景,评估DDR带宽利用率和访问延迟,为架构优化提供XXX组数据支撑。

5.低功耗验证:搭建UPF仿真流程,验证模块在不同功耗状态下的功能与隔离策略,发现并修复XXX个功耗状态转换bug。

项目业绩:

1.负责模块的功能验证在流片前XXX周全部完成,代码覆盖率XXX%,功能覆盖率XXX%。

2.发现的XXX个BUG中包含X个高级别缺陷,避免了流片后可能的功能故障。

3.验证平台与测试用例复用至后续衍生芯片项目,复用率超过XXX%。

4.通过验证阶段提出的XXX项设计优化建议,使DDR控制器实测带宽效率提升XXX%。

教育背景

GPA X.XX/X.X(专业前XX%),主修数字电路设计、微处理器系统等核心课程。参与基于FPGA的图像处理系统课程设计,在团队中负责图像采集缓存控制器Verilog代码编写与仿真测试,熟悉Modelsim仿真工具及Synopsys DC综合流程基础应用,掌握C语言与Python用于脚本开发。

自我评价

培训经历

系统学习高级UVM机制与验证方法学,将序列虚拟化、回调函数等先进技术应用于实际项目验证平台中,通过优化事务级建模与通信方式,使得测试用例的编写效率提升XXX%,平台运行速度提高约XXX%。输出的验证架构最佳实践指南,被团队采纳为新建项目的参考标准。

高级数字IC验证工程师轻商务简历模板

适用人群: #数字IC验证工程师 #高级[5-10年]

猜你想用

关于数字IC验证工程师简历的常见问题

[基本信息]

姓名:陈小湾

性别:男

年龄:26

学历:本科

婚姻:未婚

年限:4年

面貌:党员

邮箱:xiaowan@gangwan.com

电话:18600001654

[求职意向]

工作性质:全职

应聘职位:数字IC验证工程师

期望城市:北京

期望薪资:8000-10000

求职状态:离职-随时到岗

[工作经历]

北京XX科技有限公司 | 数字IC验证工程师

2024-09 - 2025-12

XXX半导体是一家专注于高性能计算芯片设计的科技公司,团队规模约XXX人,核心业务是为数据中心和智能驾驶领域提供定制化SoC解决方案,产品已成功应用于多家主流客户,年出货芯片超XXX万颗。

工作概述:

1.验证策略制定:针对复杂IP及SoC芯片规格,制定从模块到系统的多层级验证计划;分解功能点并与设计、系统部门对齐测试目标,明确覆盖率收敛标准,通过评审与迭代将验证盲区降低XXX%。

2.验证平台搭建:主导UVM验证平台的架构设计与实现,集成第三方VIP并开发定制化组件;搭建自动化编译与仿真环境,通过脚本管理将环境复用率提升至XXX%,支持多项目并行开发。

3.测试用例开发:基于验证计划编写定向测试和随机约束测试用例,构造极端场景和错误注入案例;利用脚本自动生成并归类测试,使得验证向量对关键功能的刺激完备性达到XXX%。

4.回归测试管理:建立并维护日常回归测试集,利用服务器集群实现分布式仿真;监控回归结果,分析失败用例根因,引入自动比对与打卡机机制,将问题定位平均时间缩短XXX小时。

5.覆盖率收集与分析:使用代码覆盖率与功能覆盖率双重指标驱动验证进程;定期分析覆盖率报告,针对未覆盖点补充测试或调整约束,最终推动设计sign-off覆盖率满足XXX%的目标。

6.FPGA原型验证:负责将RTL代码移植至FPGA原型验证平台,协助软件团队进行早期驱动开发和性能评估;通过实际负载测试发现深层次时序问题,提前暴露XXX类潜在风险。

7.团队协作与培训:负责指导初级验证工程师,制定模块验证任务并review代码;编写验证方法学手册与常见问题库,组织内部技术分享,帮助团队整体问题解决效率提升XXX%。

工作业绩:

1.主导完成X颗大规模SoC芯片及XX个关键IP的验证任务,保障所有负责模块按时达成sign-off标准。

2.搭建的UVM验证平台成为部门标准模板,应用于后续X个项目,平台稳定性提升XXX%。

3.通过自动化脚本将测试用例生成效率提升XXX%,累计编写和维护超过XXX个测试用例。

4.管理的回归测试框架日均运行仿真任务超XXX个,问题发现到反馈闭环时间缩短XXX%。

5.负责模块的代码与功能覆盖率均达到并超过XXX%的门限要求。

6.在FPGA原型验证阶段提前发现并协助修复XXX个RTLbug,避免流片后重大缺陷。

7.带领X人验证小组,培养X名工程师独立承担模块验证工作,输出技术文档XX份。

[项目经历]

项目名称:云端AI训练芯片XXX项目

担任角色:项目负责人

公司首颗面向数据中心的7nm AI训练芯片,集成自研张量处理单元(TPU)及高速互联接口,芯片规模超XXX亿晶体管。项目挑战在于复杂计算单元的功能正确性验证、片上网络(NoC)的通信性能验证以及低功耗设计验证,原有验证方法无法在XXX个月内完成全芯片验证收敛。

项目业绩:

1.负责模块的功能验证在流片前XXX周全部完成,代码覆盖率XXX%,功能覆盖率XXX%。

2.发现的XXX个BUG中包含X个高级别缺陷,避免了流片后可能的功能故障。

3.验证平台与测试用例复用至后续衍生芯片项目,复用率超过XXX%。

4.通过验证阶段提出的XXX项设计优化建议,使DDR控制器实测带宽效率提升XXX%。

[教育背景]

杭州电子科技大学

电子信息工程 | 本科

GPA X.XX/X.X(专业前XX%),主修数字电路设计、微处理器系统等核心课程。参与基于FPGA的图像处理系统课程设计,在团队中负责图像采集缓存控制器Verilog代码编写与仿真测试,熟悉Modelsim仿真工具及Synopsys DC综合流程基础应用,掌握C语言与Python用于脚本开发。