正在查看在校生FPGA开发严谨简历模板文字版

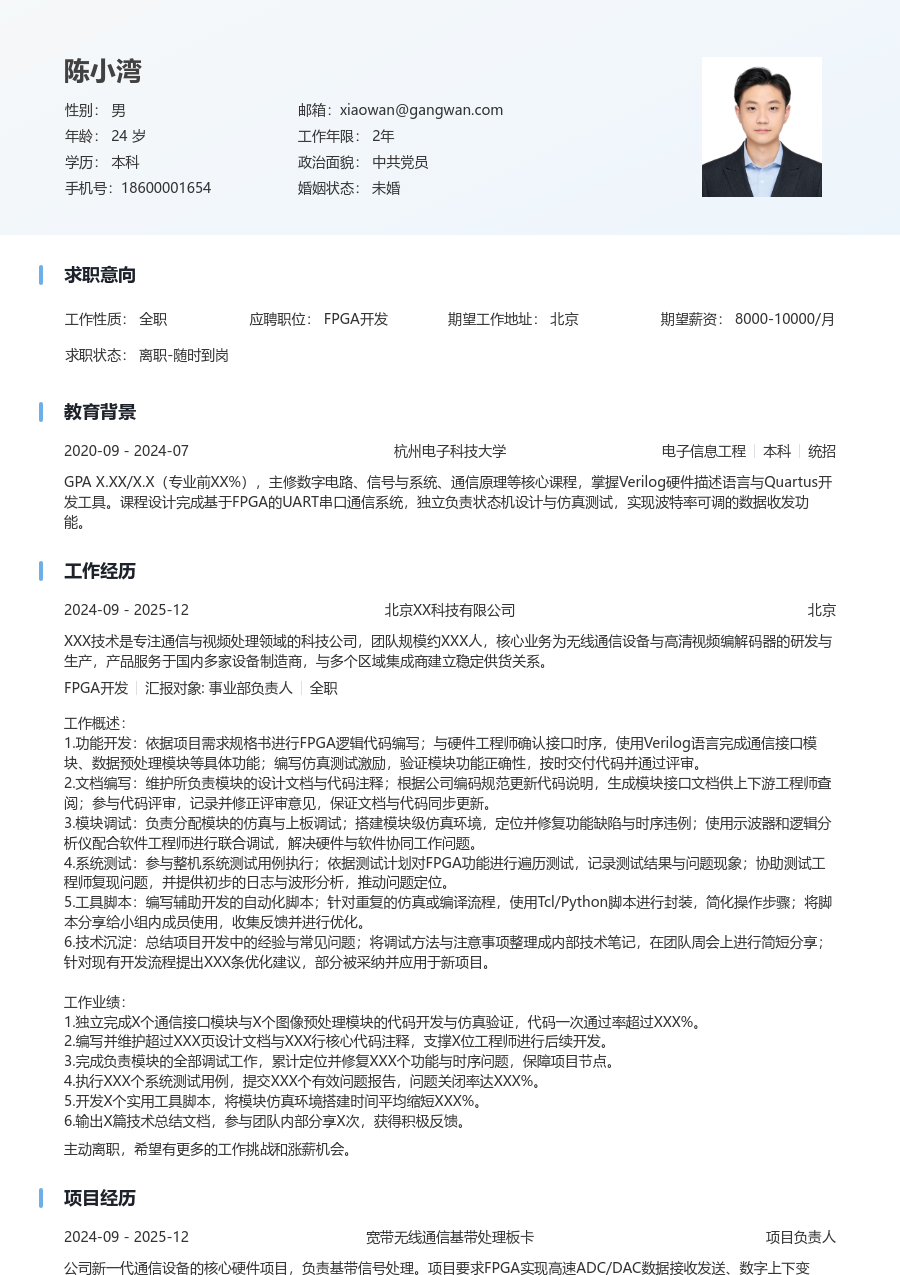

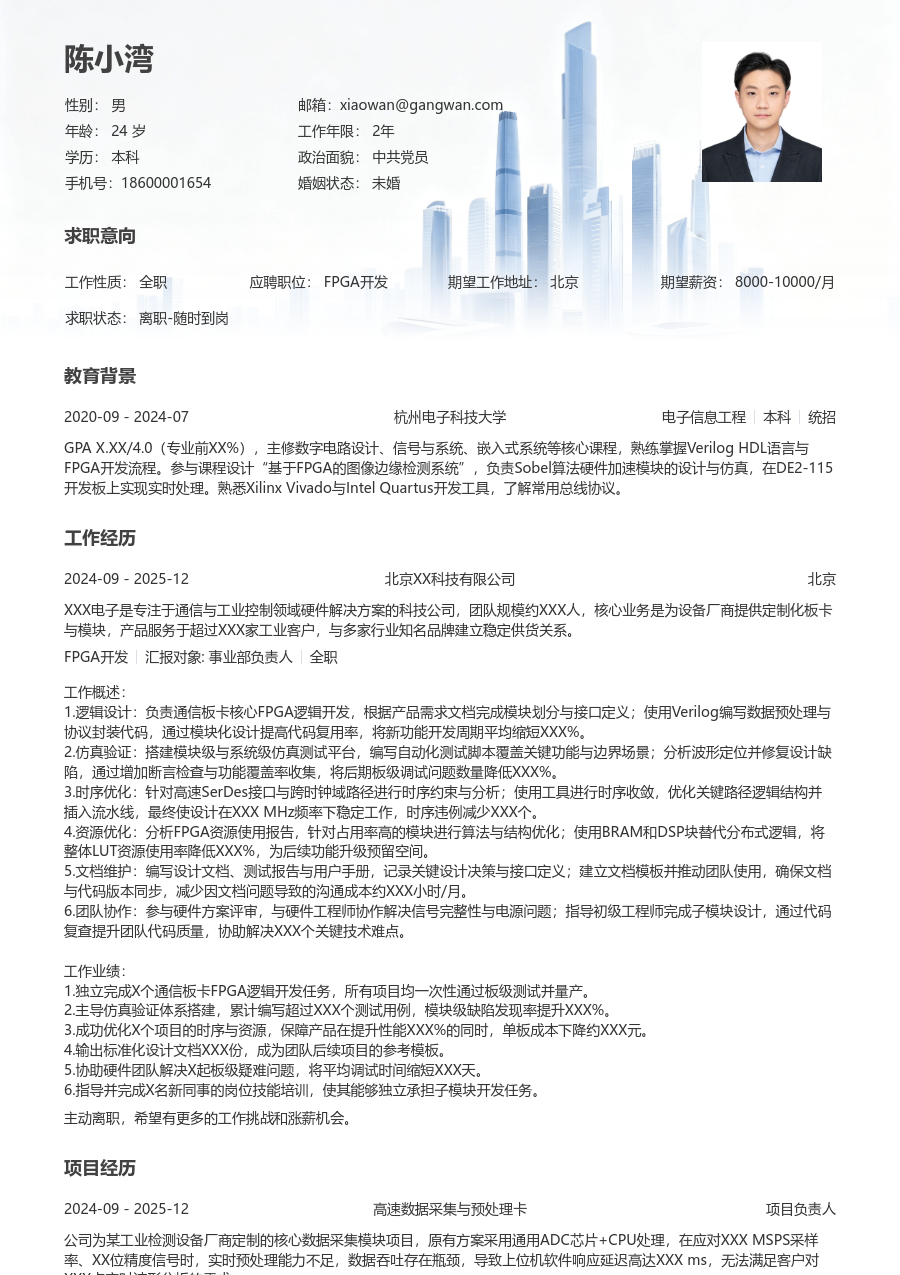

陈小湾

求职意向

工作经历

XXX电子是专注于工业自动化控制与机器视觉解决方案的硬件公司,团队规模约XXX人,核心业务是为设备制造商提供定制化嵌入式控制板卡与图像处理模组,产品应用于超过XXX个工业场景,与多家区域集成商建立长期合作。

工作概述:

1.逻辑设计:依据功能需求书完成算法向RTL代码的转换,设计关键模块如数据缓存与通信接口;使用Verilog HDL编写核心逻辑代码,通过基础仿真验证功能正确性;配合验证工程师排查问题,将模块代码一次通过率提升至XXX%。

2.仿真验证:搭建模块级测试平台,编写激励测试向量覆盖主要功能场景;使用EDA工具进行功能仿真与波形调试,定位并修复代码中的时序与逻辑错误;完善验证用例,将功能覆盖率从XXX%提升至XXX%。

3.硬件调试:参与板级调试,使用示波器与逻辑分析仪抓取FPGA管脚信号;协助分析上下电时序与接口通信异常问题,定位硬件设计与逻辑配合缺陷;通过优化复位逻辑与IO约束,解决关键信号毛刺问题,提升板卡启动成功率XXX%。

4.文档编写:负责所开发模块的设计说明文档与用户手册的撰写与维护;整理测试报告与调试记录,归档关键版本的技术资料;标准化文档模板,使团队内部资料查阅效率提升XXX%。

工作业绩:

1.独立完成X个核心功能模块的RTL设计与基础验证,代码规模约XXX行。

2.执行模块仿真测试XXX次,发现并协助修复RTL缺陷XXX个,模块功能验证周期缩短XXX%。

3.支持X款新板卡的硬件调试,定位并协助解决XX类信号完整性问题,单板调试时间减少XXX小时。

4.输出并维护技术文档XX份,资料完整度与准确性获得团队认可,支持了后续X个衍生项目的快速启动。

主动离职,希望有更多的工作挑战和涨薪机会。

项目经历

公司为某检测设备制造商定制的FPGA项目,原有方案使用通用处理器处理XXX万像素的图像数据,存在长达XXX毫秒的采集延迟,无法满足产线对实时性的要求。FPGA与Camera Link相机及DDR3内存的接口时序存在不稳定现象,在连续工作时常发生数据丢失,影响检测准确率。

项目职责:

1.模块开发:负责图像数据接收与缓存控制模块开发,设计Camera Link接口解码逻辑与DDR3读写仲裁器,实现RAW图像数据的实时接收与跨时钟域缓冲。

2.算法实现:将基础的图像预处理算法(如中值滤波、边缘提取)转化为流水线硬件结构,优化计算路径以降低资源占用。

3.协同调试:配合硬件工程师进行信号完整性测试,根据实测波形调整IO延迟参数;与软件工程师约定控制寄存器映射表,完成驱动对接。

4.测试验证:搭建系统级测试环境,利用MATLAB生成测试图像源,对比处理前后结果,验证算法硬件实现的正确性与一致性。

项目业绩:

1.系统图像采集与预处理延迟从XXX毫秒降低至XXX毫秒,满足产线XXX帧/秒的实时处理要求。

2.FPGA与相机及DDR3的接口通信稳定性达到XXX%,数据丢包问题被根除。

3.实现的硬件算法模块资源占用(LUT/BRAM)相比初始方案优化XXX%。

4.项目交付后成功应用于客户新一代设备,支撑该设备单品年销量突破XXX台。

教育背景

GPA X.XX/X.X(专业前XX%),主修数字电路与逻辑设计、嵌入式系统、信号与系统核心课程。掌握Verilog硬件描述语言与Vivado开发流程,熟悉Modelsim仿真工具。完成数字信号处理系统课程设计,负责FPGA端的FIR滤波器模块实现与功能验证,在DE1-SoC开发板上成功完成音频信号滤波演示。

自我评价

培训经历

系统学习了Xilinx 7系列FPGA架构、Vivado高级设计流程与时序收敛方法。将培训所学的时序约束与优化技巧应用于图像处理项目,通过合理设置时钟约束与优化关键路径,使设计最高运行频率提升XXX%,并总结了团队内部适用的时序分析检查清单。

在校生FPGA开发严谨简历模板

适用人群: #FPGA开发 #在校生[找实习]

关于FPGA开发简历的常见问题

[基本信息]

姓名:陈小湾

性别:男

年龄:26

学历:本科

婚姻:未婚

年限:4年

面貌:党员

邮箱:xiaowan@gangwan.com

电话:18600001654

[求职意向]

工作性质:全职

应聘职位:FPGA开发

期望城市:北京

期望薪资:8000-10000

求职状态:离职-随时到岗

[工作经历]

北京XX科技有限公司 | FPGA开发

2024-09 - 2025-12

XXX电子是专注于工业自动化控制与机器视觉解决方案的硬件公司,团队规模约XXX人,核心业务是为设备制造商提供定制化嵌入式控制板卡与图像处理模组,产品应用于超过XXX个工业场景,与多家区域集成商建立长期合作。

工作概述:

1.逻辑设计:依据功能需求书完成算法向RTL代码的转换,设计关键模块如数据缓存与通信接口;使用Verilog HDL编写核心逻辑代码,通过基础仿真验证功能正确性;配合验证工程师排查问题,将模块代码一次通过率提升至XXX%。

2.仿真验证:搭建模块级测试平台,编写激励测试向量覆盖主要功能场景;使用EDA工具进行功能仿真与波形调试,定位并修复代码中的时序与逻辑错误;完善验证用例,将功能覆盖率从XXX%提升至XXX%。

3.硬件调试:参与板级调试,使用示波器与逻辑分析仪抓取FPGA管脚信号;协助分析上下电时序与接口通信异常问题,定位硬件设计与逻辑配合缺陷;通过优化复位逻辑与IO约束,解决关键信号毛刺问题,提升板卡启动成功率XXX%。

4.文档编写:负责所开发模块的设计说明文档与用户手册的撰写与维护;整理测试报告与调试记录,归档关键版本的技术资料;标准化文档模板,使团队内部资料查阅效率提升XXX%。

工作业绩:

1.独立完成X个核心功能模块的RTL设计与基础验证,代码规模约XXX行。

2.执行模块仿真测试XXX次,发现并协助修复RTL缺陷XXX个,模块功能验证周期缩短XXX%。

3.支持X款新板卡的硬件调试,定位并协助解决XX类信号完整性问题,单板调试时间减少XXX小时。

4.输出并维护技术文档XX份,资料完整度与准确性获得团队认可,支持了后续X个衍生项目的快速启动。

[项目经历]

项目名称:高速图像采集与预处理系统

担任角色:项目负责人

公司为某检测设备制造商定制的FPGA项目,原有方案使用通用处理器处理XXX万像素的图像数据,存在长达XXX毫秒的采集延迟,无法满足产线对实时性的要求。FPGA与Camera Link相机及DDR3内存的接口时序存在不稳定现象,在连续工作时常发生数据丢失,影响检测准确率。

项目业绩:

1.系统图像采集与预处理延迟从XXX毫秒降低至XXX毫秒,满足产线XXX帧/秒的实时处理要求。

2.FPGA与相机及DDR3的接口通信稳定性达到XXX%,数据丢包问题被根除。

3.实现的硬件算法模块资源占用(LUT/BRAM)相比初始方案优化XXX%。

4.项目交付后成功应用于客户新一代设备,支撑该设备单品年销量突破XXX台。

[教育背景]

南京邮电大学

电子信息工程 | 本科

GPA X.XX/X.X(专业前XX%),主修数字电路与逻辑设计、嵌入式系统、信号与系统核心课程。掌握Verilog硬件描述语言与Vivado开发流程,熟悉Modelsim仿真工具。完成数字信号处理系统课程设计,负责FPGA端的FIR滤波器模块实现与功能验证,在DE1-SoC开发板上成功完成音频信号滤波演示。