正在查看初级模拟版图设计工程师干练简历模板文字版

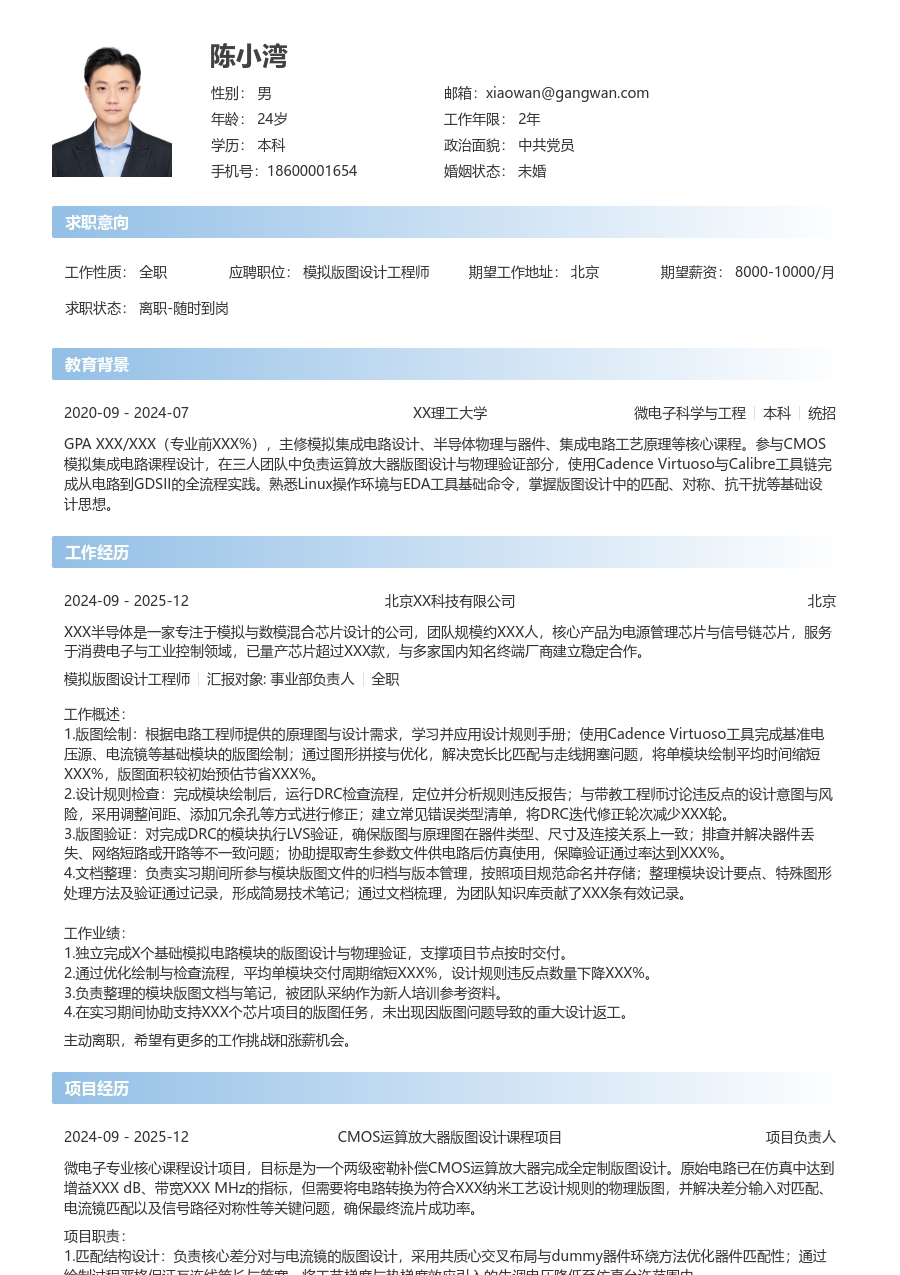

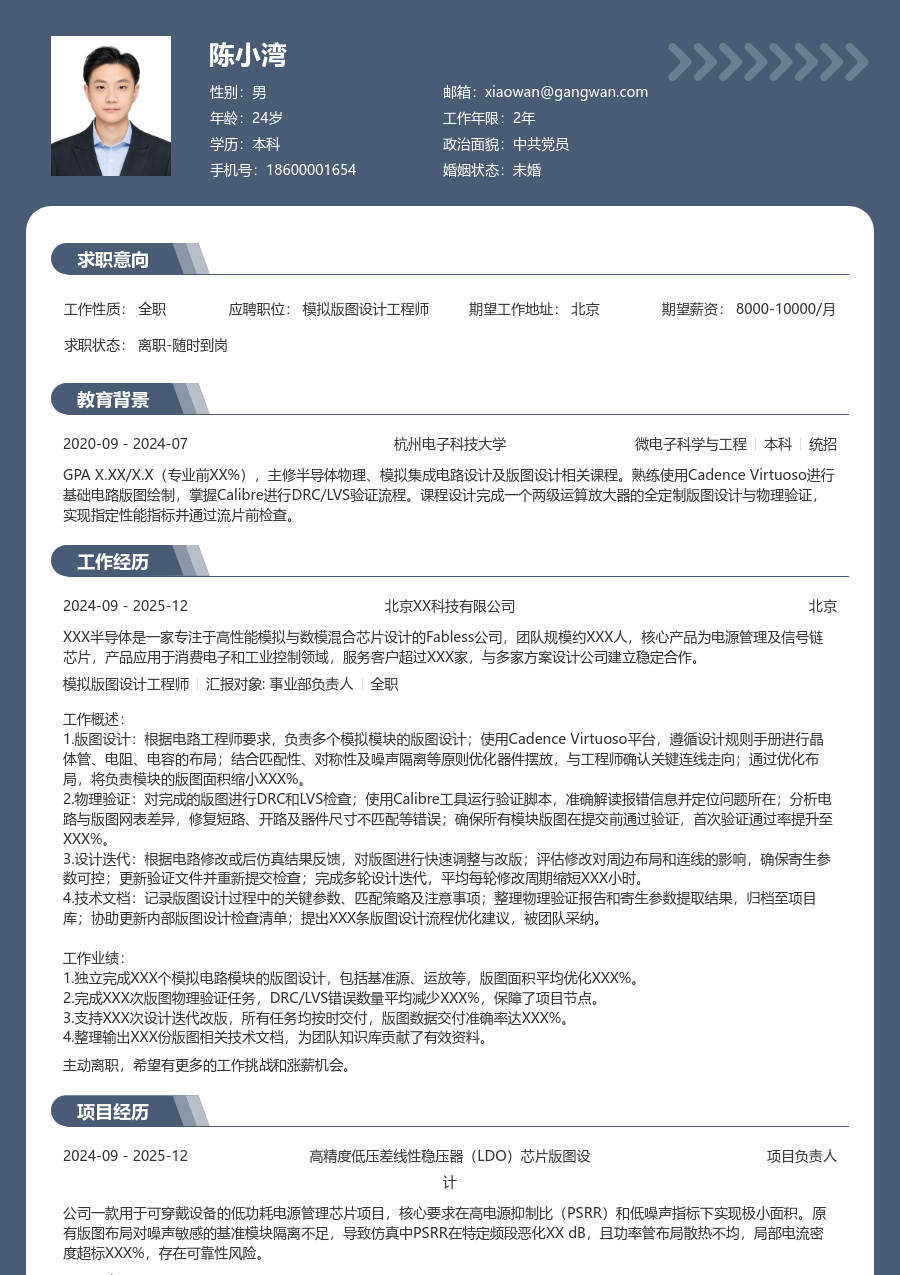

陈小湾

求职意向

工作经历

XXX半导体是一家专注于电源管理和信号链芯片设计的公司,团队规模约XXX人,核心产品为DC-DC转换器与数据转换器,服务于消费电子与工业控制领域,年出货芯片超XXX亿颗,与多家模组厂商建立了稳定的合作关系。

工作概述:

1.电路理解:接收设计工程师提供的电路原理图与规格书,通过会议沟通明确关键信号路径与匹配要求;学习并理解电路中MOS管、电阻、电容等器件的电学特性对版图的影响;记录设计要点并形成检查清单,确保后期布局符合电路意图,将因理解偏差导致的返工次数降低XXX%。

2.布局规划:根据模块功能与面积预算进行版图整体规划;确定核心器件的位置与匹配关系,规划电源线、地线及关键信号线的走线路径;使用层次化设计方法,优化模块间的连接与隔离,通过预布线分析将最终布通率提升至XXX%。

3.物理验证:完成版图绘制后,运行DRC检查工具识别工艺规则违反项;针对错误项与设计规则文档进行核对,逐一修正线宽、间距、包围等几何错误;运行LVS工具进行电路与版图一致性比对,定位并解决短路、开路及器件参数不匹配问题,保障交付版图通过率在XXX%以上。

4.可靠性设计:针对功率器件及敏感模拟电路,应用抗闩锁设计规则,增加保护环与足够的衬底接触;分析大电流路径,采用宽金属并增加通孔数量以降低寄生电阻与电迁移风险;优化关键匹配器件的版图形状与周围环境一致性,将芯片的长期可靠性测试失效率降低了XXX%。

5.数据管理:使用公司统一的版图设计平台进行数据创建与版本控制;按照项目节点要求,打包并提交GDSII数据文件及验证报告文档;维护个人工作区的文件结构清晰,记录关键设计决策与修改历史,确保数据可追溯性,版本管理错误发生次数为0。

6.工艺对接:学习并消化晶圆厂提供的工艺设计套件文档,掌握各层掩膜的定义与设计规则;参与新工艺平台导入的内部评估,绘制测试结构并反馈可制造性建议;将工艺限制转化为内部设计检查项,帮助团队规避了XXX处潜在制造缺陷。

工作业绩:

1.独立完成X颗DC-DC芯片中XXX个模拟模块的版图设计与验证,均实现首次流片即满足电气规格。

2.主导XXnm工艺下某高性能运算放大器版图项目,通过优化匹配与布线,将关键性能参数(如失调电压)改善XXX%,超出设计目标。

3.建立的个人版图设计检查清单被团队采纳,使新人培养周期平均缩短XXX周,模块集成阶段问题数减少XXX%。

4.在负责的版图任务中,平均交付周期比计划提前X天,物理验证一次通过率达到XXX%。

5.通过实施可靠性设计规则,所负责模块在后端芯片测试中未出现因版图导致的闩锁或电迁移失效案例。

主动离职,希望有更多的工作挑战和涨薪机会。

项目经历

公司新一代手机电源管理芯片的核心项目,旨在提升轻载效率并降低静态功耗。芯片采用XXXnm BCD工艺,集成大功率开关管、精密基准源与逻辑控制模块。原有版图布局中功率环路寄生电感过高导致开关噪声超标,同时模拟与数字模块间干扰影响了基准源的精度,需在XXX平方毫米的限定面积内完成全芯片版图整合与优化。

项目职责:

1.负责功率级版图设计:规划功率MOSFET与电感的布局,采用对称及叉指结构降低导通电阻与寄生电容;优化电源与地线金属层堆叠,加宽电流路径并倍增通孔,将功率环路的寄生电感降低了XXX%。

2.负责敏感模块隔离:为基准电压源与误差放大器模块设计独立的保护环与隔离阱,增加与数字开关区域的间距,并使用屏蔽层覆盖关键信号线,使电源抑制比指标提升XXXdB。

3.协调顶层集成:与项目经理及其他版图工程师协同,定义模块接口的布线通道与电源网格;整合所有子模块版图,完成顶层电源地环、Pad排列及ESD防护电路布局,确保芯片可封装性。

4.执行后仿验证支持:提取关键模块(如功率开关、振荡器)的寄生参数文件(SPEF)交付给电路工程师进行后仿真,根据仿真反馈调整连线策略,使开关节点振铃幅度减小XXX%。

项目业绩:

1.按时交付全套GDSII数据,芯片首次流片成功,功能测试通过率达XXX%。

2.通过版图优化,芯片峰值转换效率达到X

X.X%,轻载效率提升

X.X%,满足客户旗舰机型严苛的功耗要求。

3.项目量产后的芯片在客户端不良率低于XXX PPM,因版图相关的噪声与干扰问题导致的客诉为0。

4.该项目成为公司后续电源类芯片版图设计的参考案例,相关设计规范被写入部门工作手册。

教育背景

GPA X.XX/4.0(专业前XX%),主修模拟集成电路设计、半导体物理与工艺等核心课程。参与课程项目CMOS运算放大器版图设计,使用Cadence Virtuoso工具完成从电路图到DRC/LVS验证的全流程,实现了特定增益与带宽指标。熟悉Linux操作系统及IC设计基础EDA工具。

自我评价

培训经历

系统学习了模拟集成电路设计与版图的核心知识。将认证所学的系统化设计方法应用于日常项目,特别是在某DC-DC芯片项目中,通过理论计算指导功率管布局与匹配设计,避免了因经验不足导致的设计反复,使该模块版图设计周期缩短了XXX%,且后仿真结果与设计预期高度吻合。

初级模拟版图设计工程师干练简历模板

适用人群: #模拟版图设计工程师 #初级[1-3年]

猜你想用

关于模拟版图设计工程师简历的常见问题

[基本信息]

姓名:陈小湾

性别:男

年龄:26

学历:本科

婚姻:未婚

年限:4年

面貌:党员

邮箱:xiaowan@gangwan.com

电话:18600001654

[求职意向]

工作性质:全职

应聘职位:模拟版图设计工程师

期望城市:北京

期望薪资:8000-10000

求职状态:离职-随时到岗

[工作经历]

北京XX科技有限公司 | 模拟版图设计工程师

2024-09 - 2025-12

XXX半导体是一家专注于电源管理和信号链芯片设计的公司,团队规模约XXX人,核心产品为DC-DC转换器与数据转换器,服务于消费电子与工业控制领域,年出货芯片超XXX亿颗,与多家模组厂商建立了稳定的合作关系。

工作概述:

1.电路理解:接收设计工程师提供的电路原理图与规格书,通过会议沟通明确关键信号路径与匹配要求;学习并理解电路中MOS管、电阻、电容等器件的电学特性对版图的影响;记录设计要点并形成检查清单,确保后期布局符合电路意图,将因理解偏差导致的返工次数降低XXX%。

2.布局规划:根据模块功能与面积预算进行版图整体规划;确定核心器件的位置与匹配关系,规划电源线、地线及关键信号线的走线路径;使用层次化设计方法,优化模块间的连接与隔离,通过预布线分析将最终布通率提升至XXX%。

3.物理验证:完成版图绘制后,运行DRC检查工具识别工艺规则违反项;针对错误项与设计规则文档进行核对,逐一修正线宽、间距、包围等几何错误;运行LVS工具进行电路与版图一致性比对,定位并解决短路、开路及器件参数不匹配问题,保障交付版图通过率在XXX%以上。

4.可靠性设计:针对功率器件及敏感模拟电路,应用抗闩锁设计规则,增加保护环与足够的衬底接触;分析大电流路径,采用宽金属并增加通孔数量以降低寄生电阻与电迁移风险;优化关键匹配器件的版图形状与周围环境一致性,将芯片的长期可靠性测试失效率降低了XXX%。

5.数据管理:使用公司统一的版图设计平台进行数据创建与版本控制;按照项目节点要求,打包并提交GDSII数据文件及验证报告文档;维护个人工作区的文件结构清晰,记录关键设计决策与修改历史,确保数据可追溯性,版本管理错误发生次数为0。

6.工艺对接:学习并消化晶圆厂提供的工艺设计套件文档,掌握各层掩膜的定义与设计规则;参与新工艺平台导入的内部评估,绘制测试结构并反馈可制造性建议;将工艺限制转化为内部设计检查项,帮助团队规避了XXX处潜在制造缺陷。

工作业绩:

1.独立完成X颗DC-DC芯片中XXX个模拟模块的版图设计与验证,均实现首次流片即满足电气规格。

2.主导XXnm工艺下某高性能运算放大器版图项目,通过优化匹配与布线,将关键性能参数(如失调电压)改善XXX%,超出设计目标。

3.建立的个人版图设计检查清单被团队采纳,使新人培养周期平均缩短XXX周,模块集成阶段问题数减少XXX%。

4.在负责的版图任务中,平均交付周期比计划提前X天,物理验证一次通过率达到XXX%。

5.通过实施可靠性设计规则,所负责模块在后端芯片测试中未出现因版图导致的闩锁或电迁移失效案例。

[项目经历]

项目名称:高效率降压转换器芯片版图设计

担任角色:项目负责人

公司新一代手机电源管理芯片的核心项目,旨在提升轻载效率并降低静态功耗。芯片采用XXXnm BCD工艺,集成大功率开关管、精密基准源与逻辑控制模块。原有版图布局中功率环路寄生电感过高导致开关噪声超标,同时模拟与数字模块间干扰影响了基准源的精度,需在XXX平方毫米的限定面积内完成全芯片版图整合与优化。

项目业绩:

1.按时交付全套GDSII数据,芯片首次流片成功,功能测试通过率达XXX%。

2.通过版图优化,芯片峰值转换效率达到X

X.X%,轻载效率提升

X.X%,满足客户旗舰机型严苛的功耗要求。

3.项目量产后的芯片在客户端不良率低于XXX PPM,因版图相关的噪声与干扰问题导致的客诉为0。

4.该项目成为公司后续电源类芯片版图设计的参考案例,相关设计规范被写入部门工作手册。

[教育背景]

杭州电子科技大学

微电子科学与工程 | 本科

GPA X.XX/4.0(专业前XX%),主修模拟集成电路设计、半导体物理与工艺等核心课程。参与课程项目CMOS运算放大器版图设计,使用Cadence Virtuoso工具完成从电路图到DRC/LVS验证的全流程,实现了特定增益与带宽指标。熟悉Linux操作系统及IC设计基础EDA工具。