正在查看高级模拟版图设计工程师精炼简历模板文字版

陈小湾

求职意向

工作经历

XXX半导体是一家专注于电源管理及信号链芯片设计的Fabless公司,团队规模约XXX人,核心产品包括DC-DC转换器、LDO、数据转换器等,服务于消费电子、工业控制及汽车电子领域,年出货量超XXX亿颗,与多家国内主流系统厂商建立稳定合作关系。

工作概述:

1.电路分析:负责承接设计工程师提供的电路原理图,分析关键模块如基准源、运放、功率管的工作特性与匹配要求;根据工艺文档评估寄生参数对性能的影响,识别潜在的ESD和闩锁风险点,制定初步版图规划,确保后端实现与前端设计意图一致,将设计沟通反馈周期缩短XXX%。

2.版图设计:依据规划完成从晶体管到模块级的版图绘制,重点处理差分对、电流镜等需要高匹配度结构的布局与走线;采用叉指、共质心等方法优化匹配性,利用屏蔽线和保护环抑制噪声串扰与衬底耦合;执行DRC与LVS检查,确保首轮通过率达到XXX%以上。

3.模块整合:主导完成芯片顶层的模块拼接与电源地规划,规划全局电源线和信号线的走线路径与宽度,平衡电流密度与面积开销;优化压焊点(PAD)排布以符合封装要求,处理模块间接口的隔离与电平转换,通过合理的层次化设计将顶层整合时间减少XXX天。

4.数据管理:维护项目版图库与设计文档的版本,使用脚本工具批量处理GDS/OASIS等数据文件的导出与转换;协同测试工程师准备流片数据包,确保交付数据的完整性与准确性,建立数据备份与归档流程,实现XXX次流片数据零差错交付。

5.流程维护:针对新工艺节点,参与建立和优化版图设计规则检查(DRC)与电路图版图一致性检查(LVS)的规则文件;编写用于寄生参数提取(PEX)的后仿真配置文件,验证其准确性,将后仿真与硅片测试结果的偏差控制在XXX%以内。

6.技术输出:总结常见模块(如Bandgap、OPAMP)的版图设计经验,形成内部设计指南与检查清单;指导初级工程师解决版图设计中的匹配、噪声和可靠性问题,带教XXX名新人快速胜任模块设计工作。

7.项目管理:跟踪多个并行项目的版图进度,识别资源冲突与风险节点;协调设计、验证及封装团队的工作接口,推动问题闭环,保障项目按计划进入流片(Tape-out)阶段,平均项目周期缩短XXX%。

工作业绩:

1.主导完成超XXX颗芯片的模拟版图设计与验证工作,涵盖从180nm到55nm多个工艺节点,产品一次流片成功率超过XXX%。

2.通过优化匹配结构与布局布线,使关键模拟模块(如基准电压源)的性能波动降低XXX%,芯片良率提升XXX%。

3.建立的模块化版图库与设计检查流程,将重复模块的设计复用率提升XXX%,平均单项目版图设计周期缩短XXX%。

4.培养XXX名初级版图工程师成为项目骨干,团队整体设计效率提升XXX%。

5.管理的XXX个以上流片项目均按时交付,保障了客户样品验证与产品上市周期。

主动离职,希望有更多的工作挑战和涨薪机会。

项目经历

公司旗舰级信号链芯片项目,采用XXXnm BCD工艺,目标实现XX位精度与XXX KSPS采样率。项目挑战在于高精度SAR ADC模块中,电容阵列的匹配精度直接影响线性度,同时数字开关噪声会严重干扰敏感的模拟比较器。原有版图方案下,后仿真显示INL/DNL指标较前仿恶化超过X LSB,无法满足设计规格,且芯片面积存在XXX%的优化空间。

项目职责:

1.负责高精度电容阵列版图设计:分析电容失配对微分非线性(DNL)的影响模型,采用共质心布局配合虚拟(Dummy)电容结构,设计对称的布线方案以最小化梯度效应与失配。

2.负责模拟与数字域隔离设计:规划芯片的电源域与地平面分割,为高速比较器与开关电容电路设计独立的电源线与隔离保护环;采用屏蔽层隔离底层数字时钟线,将耦合到敏感模拟节点的噪声降低。

3.负责顶层电源与时钟分布网络设计:设计全局的电源网格(Power Mesh)以满足不同模块的电流需求与压降要求;优化关键采样时钟的走线路径与驱动,减小时钟偏斜(Skew)与抖动(Jitter)。

4.负责后仿真验证与迭代:主导完成寄生参数提取(PEX)与后仿真,根据后仿结果定位性能瓶颈,迭代优化电容阵列的布局与屏蔽措施,直至电学参数达标。

项目业绩:

1.版图设计完成后,提取寄生参数的后仿真结果显示,电容阵列匹配精度提升,ADC的INL/DNL指标达到±

0.5 LSB以内,满足设计目标。

2.通过优化的布局与隔离设计,芯片的信噪比(SNR)较初期版图方案提升XXX dB,有效位数(ENOB)达到XX位。

3.最终版图面积较初始规划节省XXX%,一次性通过DRC/LVS验证,流片后测试芯片功能与性能符合预期,产品顺利导入XXX家工业客户。

教育背景

GPA X.XX/4.0(专业前XX%),主修半导体物理、模拟集成电路设计、集成电路工艺原理等核心课程。参与课程项目“带隙基准电压源版图设计与仿真”,使用Cadence Virtuoso完成原理图输入、版图绘制及DRC/LVS验证,熟悉模拟版图设计全流程。掌握版图设计工具Virtuoso与验证工具Calibre的基本应用。

自我评价

培训经历

系统学习了先进工艺节点下的模拟版图设计挑战与解决方案,包括深亚微米效应、可靠性设计(DFR)与可制造性设计(DFM)。将知识应用于后续的XXXnm BCD工艺项目中,通过实施基于压力的匹配分析和天线效应预防措施,使相关模块的设计效率提升XXX%,后仿与硅片测试结果一致性提高,并主导编写了《XXX工艺版图设计检查清单》作为团队标准。

高级模拟版图设计工程师精炼简历模板

适用人群: #模拟版图设计工程师 #高级[5-10年]

猜你想用

关于模拟版图设计工程师简历的常见问题

[基本信息]

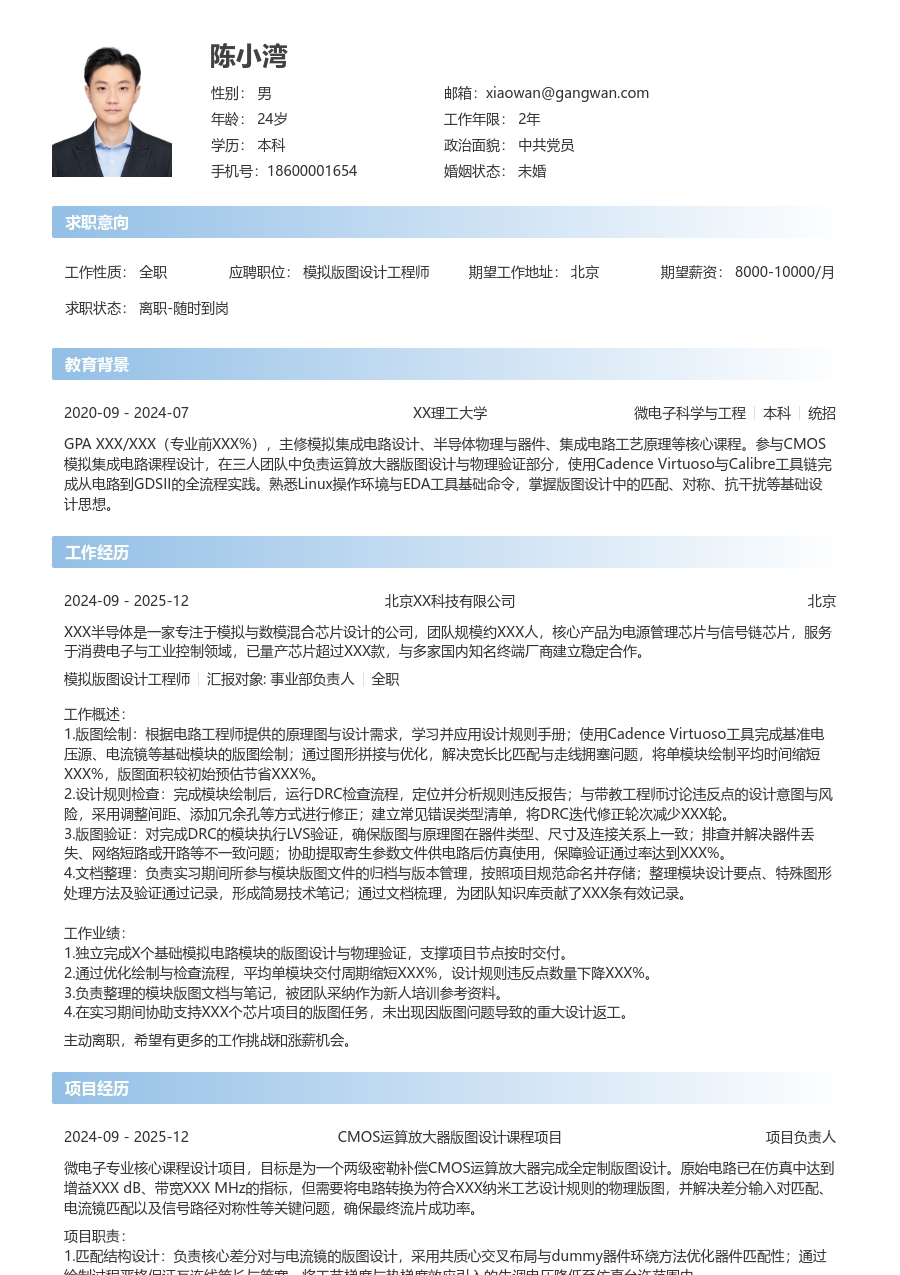

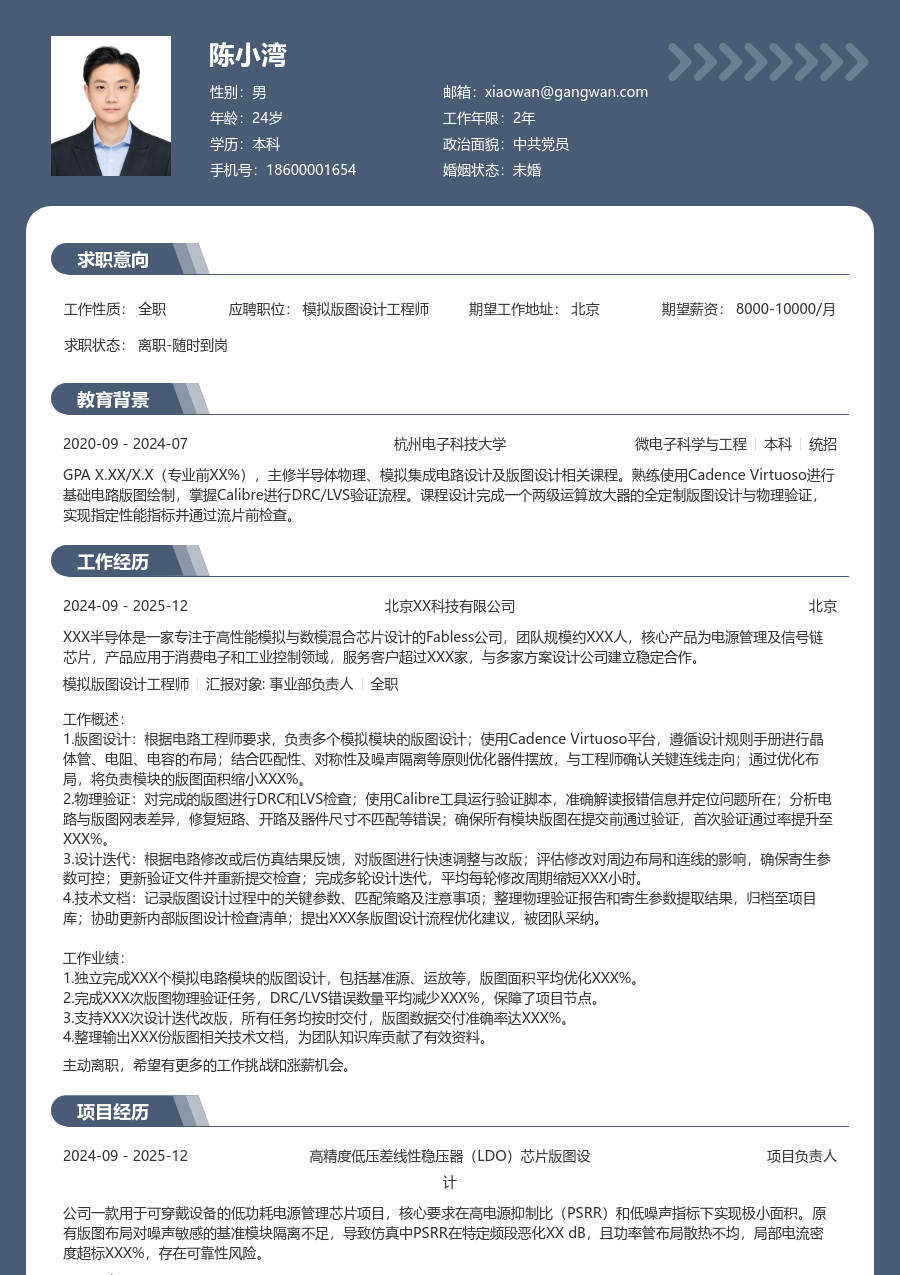

姓名:陈小湾

性别:男

年龄:26

学历:本科

婚姻:未婚

年限:4年

面貌:党员

邮箱:xiaowan@gangwan.com

电话:18600001654

[求职意向]

工作性质:全职

应聘职位:模拟版图设计工程师

期望城市:北京

期望薪资:8000-10000

求职状态:离职-随时到岗

[工作经历]

北京XX科技有限公司 | 模拟版图设计工程师

2024-09 - 2025-12

XXX半导体是一家专注于电源管理及信号链芯片设计的Fabless公司,团队规模约XXX人,核心产品包括DC-DC转换器、LDO、数据转换器等,服务于消费电子、工业控制及汽车电子领域,年出货量超XXX亿颗,与多家国内主流系统厂商建立稳定合作关系。

工作概述:

1.电路分析:负责承接设计工程师提供的电路原理图,分析关键模块如基准源、运放、功率管的工作特性与匹配要求;根据工艺文档评估寄生参数对性能的影响,识别潜在的ESD和闩锁风险点,制定初步版图规划,确保后端实现与前端设计意图一致,将设计沟通反馈周期缩短XXX%。

2.版图设计:依据规划完成从晶体管到模块级的版图绘制,重点处理差分对、电流镜等需要高匹配度结构的布局与走线;采用叉指、共质心等方法优化匹配性,利用屏蔽线和保护环抑制噪声串扰与衬底耦合;执行DRC与LVS检查,确保首轮通过率达到XXX%以上。

3.模块整合:主导完成芯片顶层的模块拼接与电源地规划,规划全局电源线和信号线的走线路径与宽度,平衡电流密度与面积开销;优化压焊点(PAD)排布以符合封装要求,处理模块间接口的隔离与电平转换,通过合理的层次化设计将顶层整合时间减少XXX天。

4.数据管理:维护项目版图库与设计文档的版本,使用脚本工具批量处理GDS/OASIS等数据文件的导出与转换;协同测试工程师准备流片数据包,确保交付数据的完整性与准确性,建立数据备份与归档流程,实现XXX次流片数据零差错交付。

5.流程维护:针对新工艺节点,参与建立和优化版图设计规则检查(DRC)与电路图版图一致性检查(LVS)的规则文件;编写用于寄生参数提取(PEX)的后仿真配置文件,验证其准确性,将后仿真与硅片测试结果的偏差控制在XXX%以内。

6.技术输出:总结常见模块(如Bandgap、OPAMP)的版图设计经验,形成内部设计指南与检查清单;指导初级工程师解决版图设计中的匹配、噪声和可靠性问题,带教XXX名新人快速胜任模块设计工作。

7.项目管理:跟踪多个并行项目的版图进度,识别资源冲突与风险节点;协调设计、验证及封装团队的工作接口,推动问题闭环,保障项目按计划进入流片(Tape-out)阶段,平均项目周期缩短XXX%。

工作业绩:

1.主导完成超XXX颗芯片的模拟版图设计与验证工作,涵盖从180nm到55nm多个工艺节点,产品一次流片成功率超过XXX%。

2.通过优化匹配结构与布局布线,使关键模拟模块(如基准电压源)的性能波动降低XXX%,芯片良率提升XXX%。

3.建立的模块化版图库与设计检查流程,将重复模块的设计复用率提升XXX%,平均单项目版图设计周期缩短XXX%。

4.培养XXX名初级版图工程师成为项目骨干,团队整体设计效率提升XXX%。

5.管理的XXX个以上流片项目均按时交付,保障了客户样品验证与产品上市周期。

[项目经历]

项目名称:用于工业控制的高精度ADC芯片版图设计

担任角色:项目负责人

公司旗舰级信号链芯片项目,采用XXXnm BCD工艺,目标实现XX位精度与XXX KSPS采样率。项目挑战在于高精度SAR ADC模块中,电容阵列的匹配精度直接影响线性度,同时数字开关噪声会严重干扰敏感的模拟比较器。原有版图方案下,后仿真显示INL/DNL指标较前仿恶化超过X LSB,无法满足设计规格,且芯片面积存在XXX%的优化空间。

项目业绩:

1.版图设计完成后,提取寄生参数的后仿真结果显示,电容阵列匹配精度提升,ADC的INL/DNL指标达到±

0.5 LSB以内,满足设计目标。

2.通过优化的布局与隔离设计,芯片的信噪比(SNR)较初期版图方案提升XXX dB,有效位数(ENOB)达到XX位。

3.最终版图面积较初始规划节省XXX%,一次性通过DRC/LVS验证,流片后测试芯片功能与性能符合预期,产品顺利导入XXX家工业客户。

[教育背景]

西安理工大学

微电子科学与工程 | 本科

GPA X.XX/4.0(专业前XX%),主修半导体物理、模拟集成电路设计、集成电路工艺原理等核心课程。参与课程项目“带隙基准电压源版图设计与仿真”,使用Cadence Virtuoso完成原理图输入、版图绘制及DRC/LVS验证,熟悉模拟版图设计全流程。掌握版图设计工具Virtuoso与验证工具Calibre的基本应用。