正在查看初级集成电路IC设计明快简历模板文字版

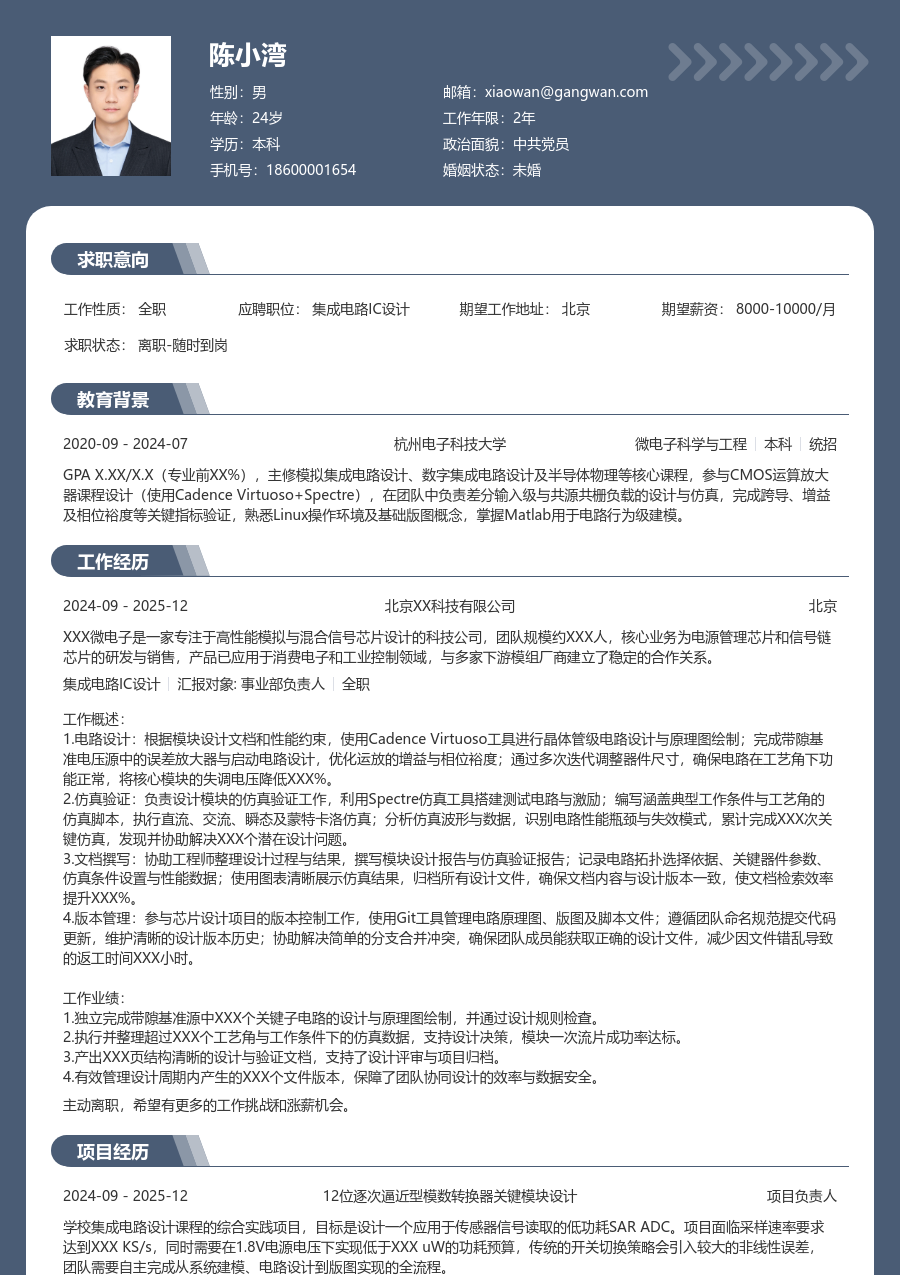

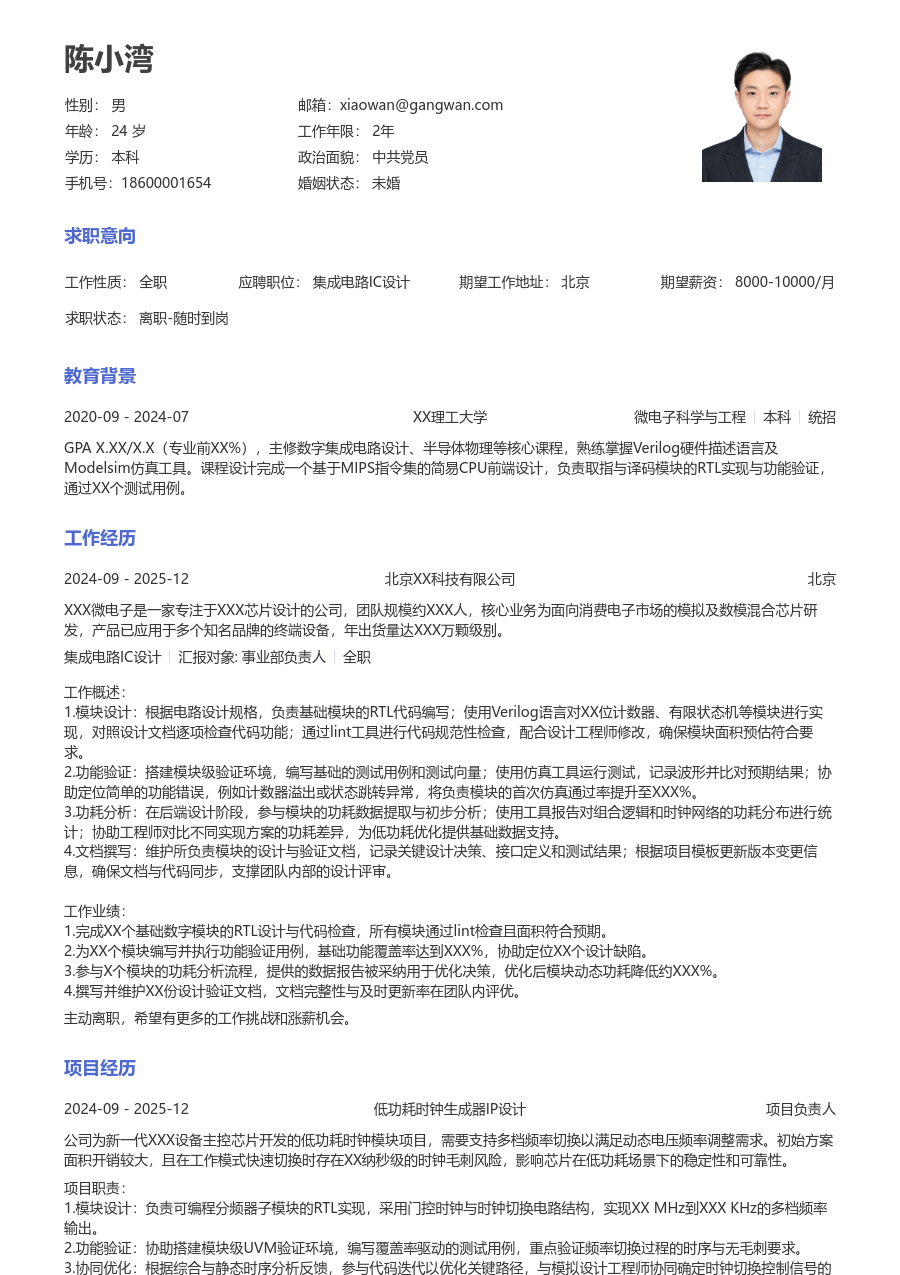

陈小湾

求职意向

工作经历

XXX半导体是一家专注于无线通信芯片设计的公司,团队规模约XXX人,核心产品为蓝牙音频SoC芯片,已成功量产并应用于多家知名消费电子品牌,年出货量达XXX万颗。

工作概述:

1.模块设计:负责芯片中特定数字功能模块的设计工作,根据架构文档使用Verilog语言完成RTL代码编写;通过阅读协议标准明确模块功能,进行初步的模块级功能验证以保障基本正确性;在设计过程中考虑面积与功耗优化,完成代码交付后支持后续验证与综合流程,所负责模块交付代码约XXX行,流片后功能正常。

2.验证支持:协助验证工程师搭建模块级测试平台,根据测试用例编写部分定向测试激励;运行仿真并协助分析波形,定位测试失败时的设计缺陷;配合修改RTL代码以修复功能问题,支持随机测试以提升覆盖率,协助将模块级功能覆盖率从XXX%提升至XXX%。

3.仿真调试:使用VCS等工具进行RTL仿真,运行验证团队提供的测试用例并记录结果;针对仿真失败用例,通过查看波形与日志文件进行初步分析,将问题定位到具体代码段后提交给资深工程师复审;维护仿真环境与脚本,确保每日回归测试稳定执行,平均每周处理仿真问题XXX个。

4.综合实现:在指导下完成模块级的逻辑综合,使用Design Compiler工具将RTL代码转换为门级网表;根据约束文件检查时序与面积报告,对不满足时序路径进行初步分析与标注;协助完成功耗估算,为芯片整体功耗优化提供数据,所负责模块综合后面积较预估减少XXX%。

5.文档撰写:负责维护所承担模块的设计文档,包括模块接口说明、功能描述与设计细节;根据设计变更实时更新文档内容,确保与代码版本一致;编写模块集成指南,支持系统工程师进行芯片集成,文档通过率与及时更新率均达XXX%。

6.流程协助:熟悉公司内部芯片设计流程与工具链,协助维护版本管理服务器上的设计代码仓库;参与设计评审会议并记录问题点,跟踪问题闭环;协助收集与整理项目中的技术数据,用于阶段性汇报,流程遵守度评价为优秀。

工作业绩:

1.独立完成X个数字模块的RTL设计,代码一次通过lint检查,设计功能符合架构要求。

2.支持验证团队完成X个模块的测试与调试工作,协助将模块级验证周期缩短XXX%。

3.处理仿真中发现的RTL问题XXX余个,问题初步定位准确率超过XXX%。

4.完成所负责模块的逻辑综合与时序分析,交付的网表满足项目预设的时钟频率目标。

5.撰写并维护设计文档XXX余份,确保设计过程可追溯,支持了团队知识积累。

6.严格遵守项目开发流程,代码提交与版本管理零失误,保障了团队协作效率。

主动离职,希望有更多的工作挑战和涨薪机会。

项目经历

公司新一代主力音频芯片项目,旨在替换已上市的老旧产品,目标是将峰值功耗降低XXX%以延长耳机续航,并集成新的音频解码算法以提升音质。项目团队约XXX人,芯片采用XXXnm工艺,设计规模约XXX万门。主要挑战在于低功耗设计、复杂时钟域管理以及紧张的XX个月流片周期。

项目职责:

1.功能开发:负责芯片电源管理单元中唤醒控制模块的RTL设计,根据功耗状态机定义完成各模式下唤醒逻辑与中断控制代码,确保模块在多种低功耗场景下功能正确。

2.验证与仿真:协助验证工程师搭建该模块的UVM测试环境,编写基础测试序列;执行大量随机测试并收集覆盖率,通过分析仿真波形协助定位并修复了X个深度休眠模式下的边界条件bug。

3.后端支持:提供模块的综合约束文件,与后端工程师沟通物理实现需求;参与模块门级网表的功能仿真与功耗分析,确保网表与RTL功能一致且功耗符合预期。

4.质量保障:参与模块级设计评审,根据反馈修改设计代码;编写模块设计文档与集成说明,确保知识传递完整;严格遵守代码签入规范与版本管理流程。

项目业绩:

1.所负责的电源管理模块一次流片成功,芯片实测待机功耗达到XXXuA的设计目标,较上一代产品降低XXX%。

2.通过积极参与验证,模块功能覆盖率最终达到XXX%,有效保障了芯片在低功耗场景下的可靠性。

3.支持项目按计划完成流片,整体开发周期控制在XX个月内,保障了产品上市时间。

教育背景

GPA X.XX/4.0(专业前XX%),主修数字电路设计、微机原理与半导体物理等核心课程,熟练掌握Verilog硬件描述语言及Modelsim仿真工具。在基于FPGA的图像处理系统课程设计中,负责图像缓存控制器的设计与调试,实现了稳定的数据流读写,项目成绩优秀。

自我评价

培训经历

系统学习了数字集成电路前端设计方法学,包括高效RTL编码风格、低功耗设计基础、静态时序分析原理及UVM验证入门。将培训所学的代码检查规范应用于实际工作,使个人编写代码的lint通过率提升至XXX%;并在低功耗蓝牙音频芯片项目中,应用门控时钟设计思想优化了负责模块的动态功耗。

初级集成电路IC设计明快简历模板

适用人群: #集成电路IC设计 #初级[1-3年]

猜你想用

关于集成电路IC设计简历的常见问题

[基本信息]

姓名:陈小湾

性别:男

年龄:26

学历:本科

婚姻:未婚

年限:4年

面貌:党员

邮箱:xiaowan@gangwan.com

电话:18600001654

[求职意向]

工作性质:全职

应聘职位:集成电路IC设计

期望城市:北京

期望薪资:8000-10000

求职状态:离职-随时到岗

[工作经历]

北京XX科技有限公司 | 集成电路IC设计

2024-09 - 2025-12

XXX半导体是一家专注于无线通信芯片设计的公司,团队规模约XXX人,核心产品为蓝牙音频SoC芯片,已成功量产并应用于多家知名消费电子品牌,年出货量达XXX万颗。

工作概述:

1.模块设计:负责芯片中特定数字功能模块的设计工作,根据架构文档使用Verilog语言完成RTL代码编写;通过阅读协议标准明确模块功能,进行初步的模块级功能验证以保障基本正确性;在设计过程中考虑面积与功耗优化,完成代码交付后支持后续验证与综合流程,所负责模块交付代码约XXX行,流片后功能正常。

2.验证支持:协助验证工程师搭建模块级测试平台,根据测试用例编写部分定向测试激励;运行仿真并协助分析波形,定位测试失败时的设计缺陷;配合修改RTL代码以修复功能问题,支持随机测试以提升覆盖率,协助将模块级功能覆盖率从XXX%提升至XXX%。

3.仿真调试:使用VCS等工具进行RTL仿真,运行验证团队提供的测试用例并记录结果;针对仿真失败用例,通过查看波形与日志文件进行初步分析,将问题定位到具体代码段后提交给资深工程师复审;维护仿真环境与脚本,确保每日回归测试稳定执行,平均每周处理仿真问题XXX个。

4.综合实现:在指导下完成模块级的逻辑综合,使用Design Compiler工具将RTL代码转换为门级网表;根据约束文件检查时序与面积报告,对不满足时序路径进行初步分析与标注;协助完成功耗估算,为芯片整体功耗优化提供数据,所负责模块综合后面积较预估减少XXX%。

5.文档撰写:负责维护所承担模块的设计文档,包括模块接口说明、功能描述与设计细节;根据设计变更实时更新文档内容,确保与代码版本一致;编写模块集成指南,支持系统工程师进行芯片集成,文档通过率与及时更新率均达XXX%。

6.流程协助:熟悉公司内部芯片设计流程与工具链,协助维护版本管理服务器上的设计代码仓库;参与设计评审会议并记录问题点,跟踪问题闭环;协助收集与整理项目中的技术数据,用于阶段性汇报,流程遵守度评价为优秀。

工作业绩:

1.独立完成X个数字模块的RTL设计,代码一次通过lint检查,设计功能符合架构要求。

2.支持验证团队完成X个模块的测试与调试工作,协助将模块级验证周期缩短XXX%。

3.处理仿真中发现的RTL问题XXX余个,问题初步定位准确率超过XXX%。

4.完成所负责模块的逻辑综合与时序分析,交付的网表满足项目预设的时钟频率目标。

5.撰写并维护设计文档XXX余份,确保设计过程可追溯,支持了团队知识积累。

6.严格遵守项目开发流程,代码提交与版本管理零失误,保障了团队协作效率。

[项目经历]

项目名称:低功耗蓝牙音频SoC芯片

担任角色:项目负责人

公司新一代主力音频芯片项目,旨在替换已上市的老旧产品,目标是将峰值功耗降低XXX%以延长耳机续航,并集成新的音频解码算法以提升音质。项目团队约XXX人,芯片采用XXXnm工艺,设计规模约XXX万门。主要挑战在于低功耗设计、复杂时钟域管理以及紧张的XX个月流片周期。

项目业绩:

1.所负责的电源管理模块一次流片成功,芯片实测待机功耗达到XXXuA的设计目标,较上一代产品降低XXX%。

2.通过积极参与验证,模块功能覆盖率最终达到XXX%,有效保障了芯片在低功耗场景下的可靠性。

3.支持项目按计划完成流片,整体开发周期控制在XX个月内,保障了产品上市时间。

[教育背景]

杭州电子科技大学

电子信息工程 | 本科

GPA X.XX/4.0(专业前XX%),主修数字电路设计、微机原理与半导体物理等核心课程,熟练掌握Verilog硬件描述语言及Modelsim仿真工具。在基于FPGA的图像处理系统课程设计中,负责图像缓存控制器的设计与调试,实现了稳定的数据流读写,项目成绩优秀。