正在查看在校生数字前端设计师时尚简历模板文字版

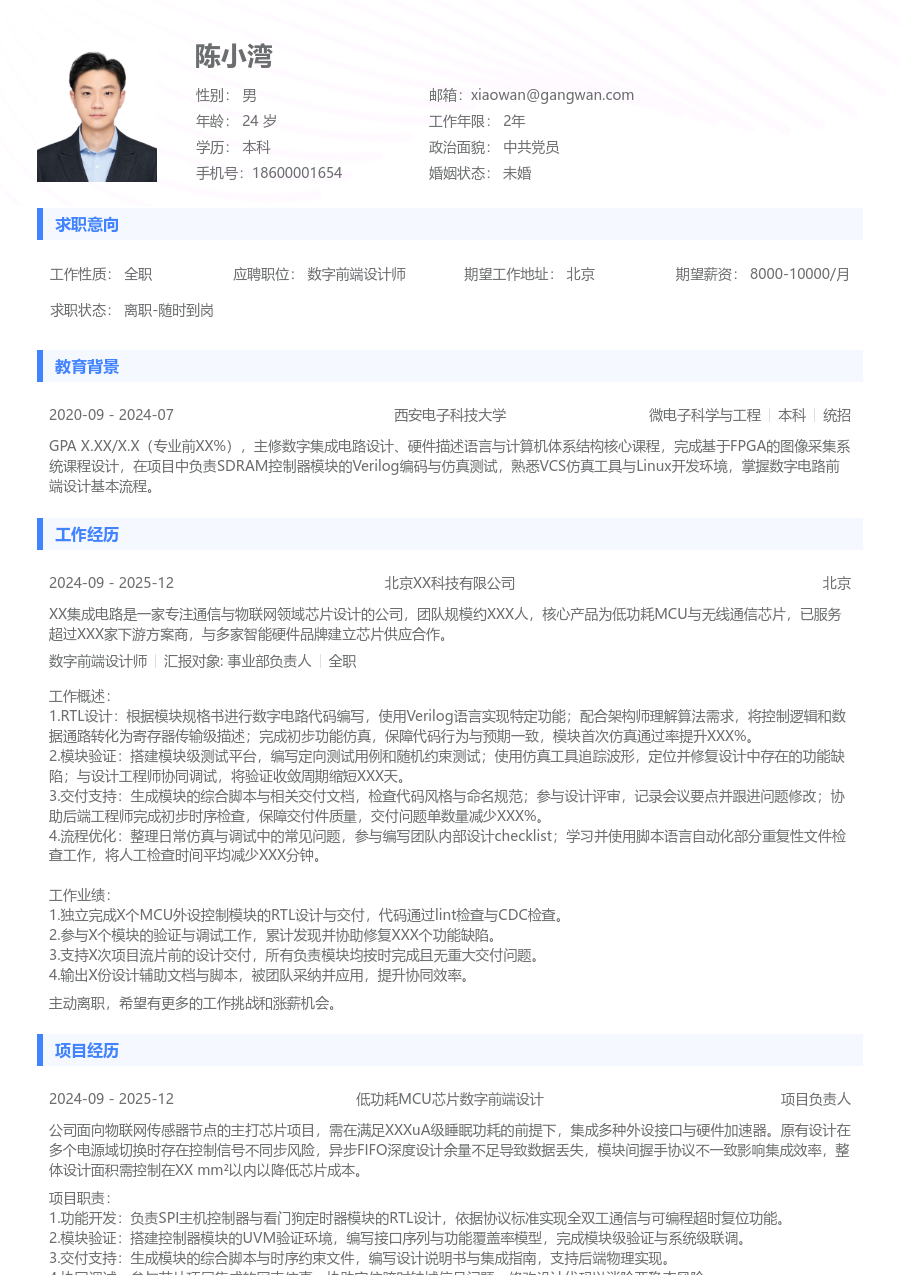

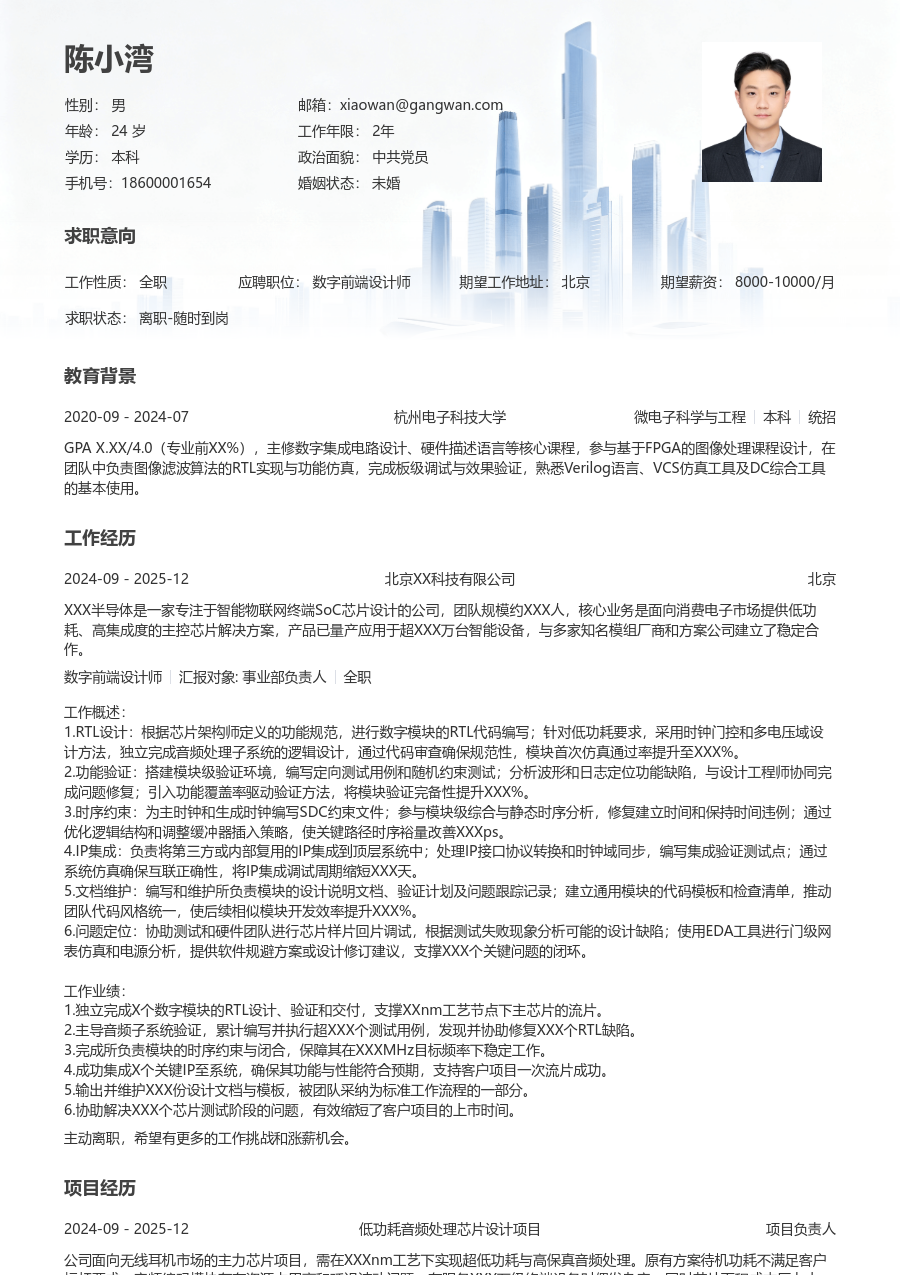

陈小湾

求职意向

工作经历

XXX集成电路是专注高性能计算芯片设计的科技公司,团队规模约XXX人,核心业务是面向数据中心和人工智能领域提供自主可控的芯片解决方案,已完成XXX款芯片的流片与量产,与多家国内领先的服务器厂商建立了合作关系。

工作概述:

1.芯片验证:参与XXX计算芯片模块级功能验证,根据设计规格文档编写基础测试用例;使用脚本自动化执行测试,记录波形并分析功能是否正确;对比验证报告与预期结果,定位并提交初步问题描述,将模块验证完成时间提前XXX天。

2.代码编写:协助资深工程师完成部分RTL代码的编写与修改,主要涉及接口逻辑与简单状态机;使用版本管理工具提交代码,配合代码走查流程,根据反馈意见调整代码风格,确保代码通过基础语法与规则检查。

3.文档整理:负责项目技术文档的归档与更新,包括验证计划、接口协议和会议纪要;建立文档索引目录,定期同步至团队共享知识库,使得相关文档查找时间平均缩短XXX%。

4.技术支持:在工程师指导下,使用EDA工具进行基础的门级网表仿真与功耗预估分析;协助整理仿真环境所需的文件与脚本,维护工具运行日志,及时反馈环境异常,支持了XXX个模块的顺利交付。

工作业绩:

1.独立完成XXX个模块的基础功能验证,累计执行测试用例XXX条,协助发现潜在设计问题XXX个。

2.参与编写与维护约XXX行可综合的RTL代码,所有提交均通过团队代码审查。

3.系统化整理项目文档XXX余份,知识库访问量累计超过XXX次,支持了团队新人的快速融入。

4.有效维护仿真环境,保障了平均每周XXX次仿真任务的成功运行,工具问题响应时间缩短XXX%。

主动离职,希望有更多的工作挑战和涨薪机会。

项目经历

课程团队项目,目标是设计一个支持基本图像滤波算法的硬件IP核。初始方案采用纯组合逻辑导致关键路径延迟过长,无法满足目标时钟频率XXX MHz的要求,同时资源利用率预估超标XXX%,在集成到更大型的SoC系统中面临时序收敛难题。

项目职责:

1.架构协助:在导师指导下理解图像滤波算法,参与将串行软件算法转换为并行硬件流水线结构的讨论,协助绘制模块数据流图。

2.逻辑设计:负责设计中值滤波模块的RTL实现,采用三级流水线结构优化关键路径,使用寄存器平衡技术将路径延迟降低XXX%。

3.功能仿真:搭建模块级仿真测试平台,编写定向测试用例与随机测试向量,验证功能正确性并与MATLAB模型输出进行对比。

4.面积优化:分析综合报告中的资源使用情况,提出将部分通用乘法器替换为移位加法的优化方案,并在验证后实施。

项目业绩:

1.最终设计在XXX工艺库下综合,最高工作频率达到XXX MHz,满足预设性能目标。

2.优化后的模块面积减少约XXX%,整体IP核资源利用率降低XXX%。

3.模块功能验证通过率达到XXX%,未发现重大逻辑缺陷。

4.项目设计报告与代码获评课程优秀项目,为后续更复杂的视频处理IP设计积累了基础框架。

教育背景

GPA X.XX/X.X(专业前XX%),主修数字集成电路设计、硬件描述语言与计算机体系结构核心课程。参与基于FPGA的简易CPU课程设计,在团队中负责算术逻辑单元模块的Verilog编码与功能仿真,成功在开发板上运行测试程序。熟悉Linux操作环境、VCS仿真工具及DC综合流程的基本使用。

自我评价

培训经历

系统学习了数字前端设计全流程,包括RTL设计、功能验证、逻辑综合与形式验证。将知识应用于图像处理IP核项目,通过采用规范的代码风格与验证方法,使模块首次集成通过率提升,并依据综合报告进行了有效的面积优化尝试。

在校生数字前端设计师时尚简历模板

适用人群: #数字前端设计师 #在校生[找实习]

猜你想用

关于数字前端设计师简历的常见问题

[基本信息]

姓名:陈小湾

性别:男

年龄:26

学历:本科

婚姻:未婚

年限:4年

面貌:党员

邮箱:xiaowan@gangwan.com

电话:18600001654

[求职意向]

工作性质:全职

应聘职位:数字前端设计师

期望城市:北京

期望薪资:8000-10000

求职状态:离职-随时到岗

[工作经历]

北京XX科技有限公司 | 数字前端设计师

2024-09 - 2025-12

XXX集成电路是专注高性能计算芯片设计的科技公司,团队规模约XXX人,核心业务是面向数据中心和人工智能领域提供自主可控的芯片解决方案,已完成XXX款芯片的流片与量产,与多家国内领先的服务器厂商建立了合作关系。

工作概述:

1.芯片验证:参与XXX计算芯片模块级功能验证,根据设计规格文档编写基础测试用例;使用脚本自动化执行测试,记录波形并分析功能是否正确;对比验证报告与预期结果,定位并提交初步问题描述,将模块验证完成时间提前XXX天。

2.代码编写:协助资深工程师完成部分RTL代码的编写与修改,主要涉及接口逻辑与简单状态机;使用版本管理工具提交代码,配合代码走查流程,根据反馈意见调整代码风格,确保代码通过基础语法与规则检查。

3.文档整理:负责项目技术文档的归档与更新,包括验证计划、接口协议和会议纪要;建立文档索引目录,定期同步至团队共享知识库,使得相关文档查找时间平均缩短XXX%。

4.技术支持:在工程师指导下,使用EDA工具进行基础的门级网表仿真与功耗预估分析;协助整理仿真环境所需的文件与脚本,维护工具运行日志,及时反馈环境异常,支持了XXX个模块的顺利交付。

工作业绩:

1.独立完成XXX个模块的基础功能验证,累计执行测试用例XXX条,协助发现潜在设计问题XXX个。

2.参与编写与维护约XXX行可综合的RTL代码,所有提交均通过团队代码审查。

3.系统化整理项目文档XXX余份,知识库访问量累计超过XXX次,支持了团队新人的快速融入。

4.有效维护仿真环境,保障了平均每周XXX次仿真任务的成功运行,工具问题响应时间缩短XXX%。

[项目经历]

项目名称:图像处理IP核前端设计

担任角色:项目负责人

课程团队项目,目标是设计一个支持基本图像滤波算法的硬件IP核。初始方案采用纯组合逻辑导致关键路径延迟过长,无法满足目标时钟频率XXX MHz的要求,同时资源利用率预估超标XXX%,在集成到更大型的SoC系统中面临时序收敛难题。

项目业绩:

1.最终设计在XXX工艺库下综合,最高工作频率达到XXX MHz,满足预设性能目标。

2.优化后的模块面积减少约XXX%,整体IP核资源利用率降低XXX%。

3.模块功能验证通过率达到XXX%,未发现重大逻辑缺陷。

4.项目设计报告与代码获评课程优秀项目,为后续更复杂的视频处理IP设计积累了基础框架。

[教育背景]

杭州电子科技大学

微电子科学与工程 | 本科

GPA X.XX/X.X(专业前XX%),主修数字集成电路设计、硬件描述语言与计算机体系结构核心课程。参与基于FPGA的简易CPU课程设计,在团队中负责算术逻辑单元模块的Verilog编码与功能仿真,成功在开发板上运行测试程序。熟悉Linux操作环境、VCS仿真工具及DC综合流程的基本使用。