正在查看应届生数字后端工程师规范简历模板文字版

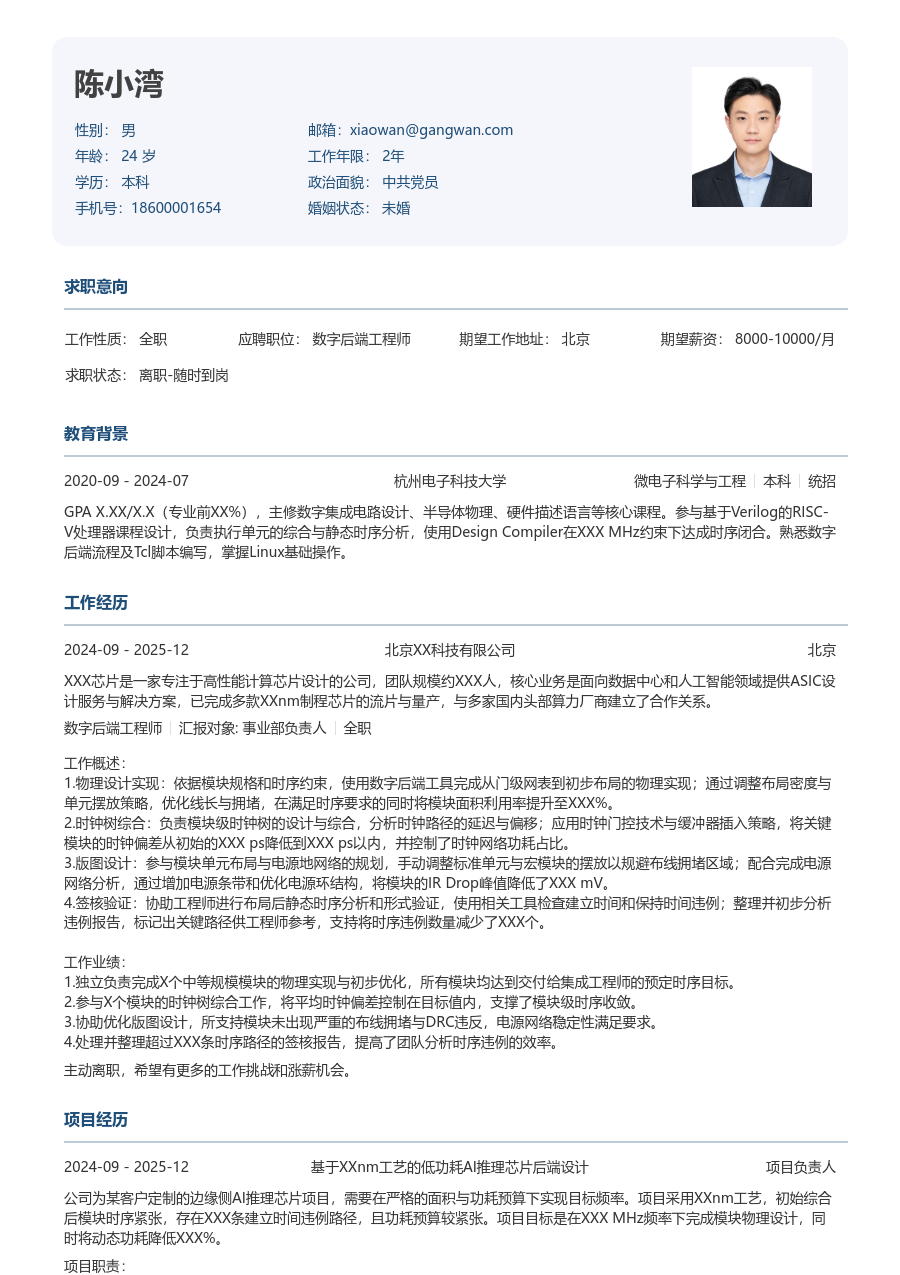

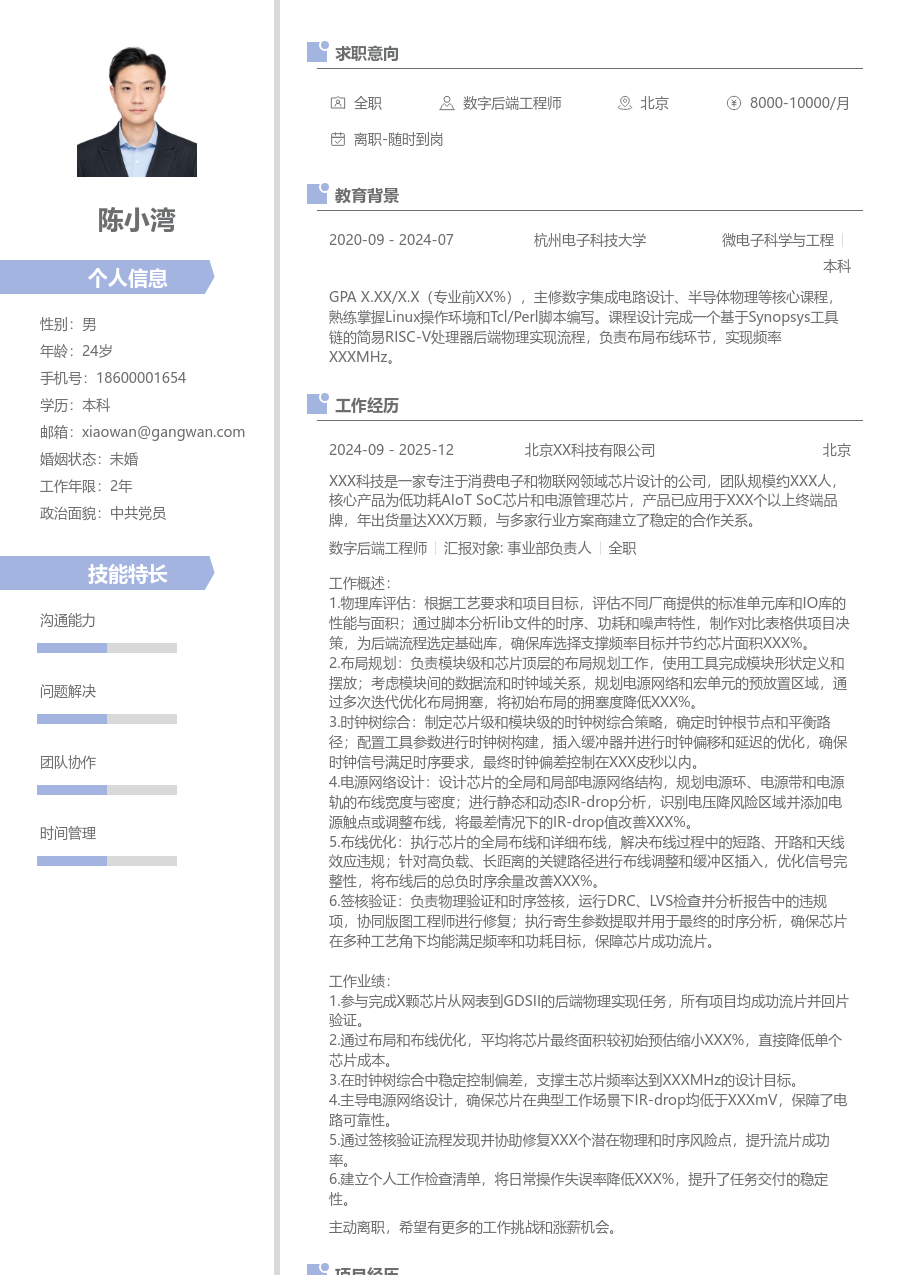

陈小湾

求职意向

工作经历

XXX半导体是一家专注于高性能模拟与混合信号芯片设计的公司,团队规模约XXX人,核心业务是为工业控制与物联网领域提供核心芯片解决方案,产品已应用于超过XXX家客户,与多家头部模组厂商建立了稳定的合作关系。

工作概述:

1.物理设计:根据前端提供的网表和设计约束,负责模块级芯片的物理实现;使用布局布线工具完成标准单元的摆放与连线,优化绕线拥塞;执行时钟树综合,确保时钟信号到达时间满足要求;通过多次迭代优化,将模块的最终时序违规数量减少了XXX%。

2.功耗签核:参与芯片功耗完整性的验证工作;使用专用工具进行静态功耗分析和动态功耗仿真;依据分析结果定位高功耗单元,并与设计工程师讨论优化方案;建立模块级功耗检查清单,将功耗签核阶段发现的问题数量降低了XXX%。

3.时序收敛:协助资深工程师进行模块的时序分析与修复;使用静态时序分析工具检查建立时间与保持时间是否达标;编写脚本自动提取关键路径的时序报告,辅助定位违例原因;通过参与XXX次时序迭代,将关键路径的负时序余量平均改善了XXXps。

4.数据交付:负责整理并交付物理设计阶段产生的各项数据文件,包括版图文件、时序库文件等;严格按照公司数据管理流程进行版本控制和归档;检查交付文件的完整性与准确性,确保流片数据包零差错。

工作业绩:

1.独立完成X个中等规模模块的物理设计与交付,全部通过签核检查,支持了X款芯片的流片。

2.参与的功耗分析工作,帮助识别并优化了X个潜在的高功耗风险点,预估贡献了整体功耗XXX%的下降。

3.通过脚本辅助时序分析,将报告生成效率提升了约XXX%,支持团队更快完成时序收敛。

4.负责交付的所有数据包均准确无误,保障了项目后端流程的顺利进行。

主动离职,希望有更多的工作挑战和涨薪机会。

项目经历

公司针对智能家居市场研发的一款关键芯片项目,采用XXX纳米工艺,集成射频与数字基带。项目挑战在于数字核心模块需在极低电压下工作以满足严苛的功耗预算,同时面积受限,布局布线难度大,初始版本在物理实现后存在大量时序违例与功耗超标问题。

项目职责:

1.模块布局规划:负责数字控制模块的物理布局,依据数据流与模块间信号交互关系,与团队共同确定模块形状与引脚位置;使用布局工具手动调整关键单元的预摆放,将模块内部总线走线长度缩短了约XXX微米。

2.功耗结构实现:根据设计需求,在工具中配置并实施多电压域与电源关断方案;绘制电源网络,确保电源完整性;检查标准单元与宏模块的电源连接正确性,完成相关物理验证。

3.时序辅助分析:协助执行模块级静态时序分析,使用脚本批量处理不同工作模式与工艺角下的时序报告;整理分析结果,将违例路径按严重程度分类并提交给负责人,提高了问题定位效率。

4.物理验证支持:参与设计规则检查与版图与原理图一致性检查的调试工作;根据工具报错信息,协助定位并修正金属间距、天线效应等常见物理违规,累计清理了XXX条违规。

项目业绩:

1.项目最终流片成功,数字核心模块在目标频率下达成时序闭合,面积较初版规划节省了XXX%。

2.通过有效的低功耗设计实现,芯片在待机模式下的实测功耗达到设计要求,低于XXX微瓦。

3.项目按时交付后端数据包,保障了整体项目周期,芯片已进入客户样品测试阶段。

教育背景

GPA X.XX/4.0(专业前XX%),主修数字集成电路设计、半导体物理与器件、硬件描述语言等核心课程。参与基于FPGA的图像处理系统课程设计,在团队中负责时序约束与系统集成,实现了XXfps的图像处理速率。熟练掌握数字后端基本流程,能使用业界主流EDA工具进行基础操作,了解Tcl脚本语言。

自我评价

培训经历

系统完成了基于XXX纳米工艺的数字芯片后端全流程实训。使用业界标准工具链,独立完成了从一个给定网表开始,经过布局规划、时钟树综合、布线、时序签核到最终生成GDSII版图文件的完整过程。实训项目最终实现了时序闭合,并理解了物理设计中的典型挑战与优化思路。

应届生数字后端工程师规范简历模板

适用人群: #数字后端工程师 #应届生[<1年]

猜你想用

关于数字后端工程师简历的常见问题

[基本信息]

姓名:陈小湾

性别:男

年龄:26

学历:本科

婚姻:未婚

年限:4年

面貌:党员

邮箱:xiaowan@gangwan.com

电话:18600001654

[求职意向]

工作性质:全职

应聘职位:数字后端工程师

期望城市:北京

期望薪资:8000-10000

求职状态:离职-随时到岗

[工作经历]

北京XX科技有限公司 | 数字后端工程师

2024-09 - 2025-12

XXX半导体是一家专注于高性能模拟与混合信号芯片设计的公司,团队规模约XXX人,核心业务是为工业控制与物联网领域提供核心芯片解决方案,产品已应用于超过XXX家客户,与多家头部模组厂商建立了稳定的合作关系。

工作概述:

1.物理设计:根据前端提供的网表和设计约束,负责模块级芯片的物理实现;使用布局布线工具完成标准单元的摆放与连线,优化绕线拥塞;执行时钟树综合,确保时钟信号到达时间满足要求;通过多次迭代优化,将模块的最终时序违规数量减少了XXX%。

2.功耗签核:参与芯片功耗完整性的验证工作;使用专用工具进行静态功耗分析和动态功耗仿真;依据分析结果定位高功耗单元,并与设计工程师讨论优化方案;建立模块级功耗检查清单,将功耗签核阶段发现的问题数量降低了XXX%。

3.时序收敛:协助资深工程师进行模块的时序分析与修复;使用静态时序分析工具检查建立时间与保持时间是否达标;编写脚本自动提取关键路径的时序报告,辅助定位违例原因;通过参与XXX次时序迭代,将关键路径的负时序余量平均改善了XXXps。

4.数据交付:负责整理并交付物理设计阶段产生的各项数据文件,包括版图文件、时序库文件等;严格按照公司数据管理流程进行版本控制和归档;检查交付文件的完整性与准确性,确保流片数据包零差错。

工作业绩:

1.独立完成X个中等规模模块的物理设计与交付,全部通过签核检查,支持了X款芯片的流片。

2.参与的功耗分析工作,帮助识别并优化了X个潜在的高功耗风险点,预估贡献了整体功耗XXX%的下降。

3.通过脚本辅助时序分析,将报告生成效率提升了约XXX%,支持团队更快完成时序收敛。

4.负责交付的所有数据包均准确无误,保障了项目后端流程的顺利进行。

[项目经历]

项目名称:低功耗物联网通信芯片后端设计

担任角色:项目负责人

公司针对智能家居市场研发的一款关键芯片项目,采用XXX纳米工艺,集成射频与数字基带。项目挑战在于数字核心模块需在极低电压下工作以满足严苛的功耗预算,同时面积受限,布局布线难度大,初始版本在物理实现后存在大量时序违例与功耗超标问题。

项目业绩:

1.项目最终流片成功,数字核心模块在目标频率下达成时序闭合,面积较初版规划节省了XXX%。

2.通过有效的低功耗设计实现,芯片在待机模式下的实测功耗达到设计要求,低于XXX微瓦。

3.项目按时交付后端数据包,保障了整体项目周期,芯片已进入客户样品测试阶段。

[教育背景]

杭州电子科技大学

电子信息工程 | 本科

GPA X.XX/4.0(专业前XX%),主修数字集成电路设计、半导体物理与器件、硬件描述语言等核心课程。参与基于FPGA的图像处理系统课程设计,在团队中负责时序约束与系统集成,实现了XXfps的图像处理速率。熟练掌握数字后端基本流程,能使用业界主流EDA工具进行基础操作,了解Tcl脚本语言。